A

B

C

D

E

F

G

H

I

J

K

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

A

B

C

D

E

F

G

H

I

J

K

C10

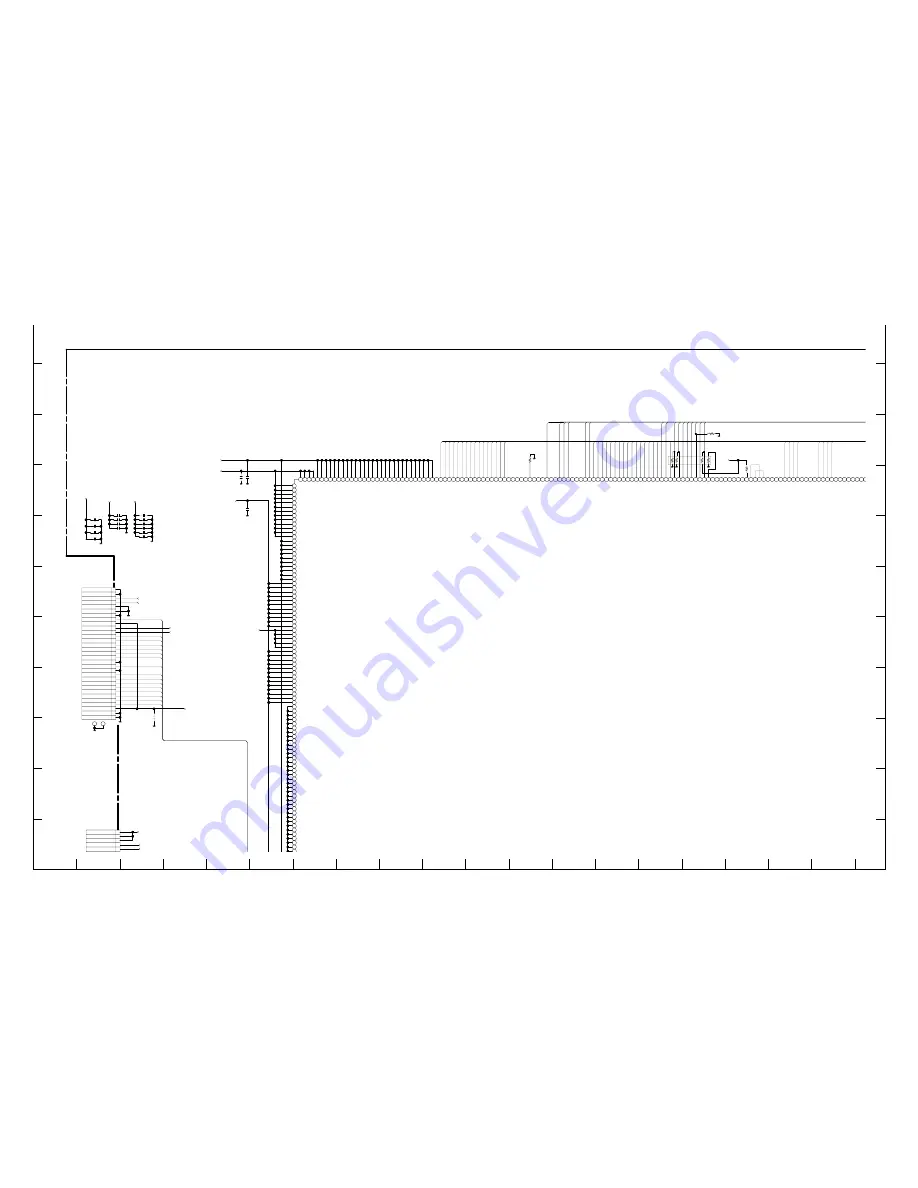

CP1 BOARD (DMA) MAIN [UPPER-LEFT]

VDD1.8

VDD1.0

VDD1.0

VDD1.8

VDD3

VDD3

0.1;B

C1051

0.1;B

C1054

0.1;B

C1052

0.1;B

C1056

0.1;B

C1055

0.1;B

C1053

C1064

0.1;B

C1063

0.1;B

C1068

0.1;B

C1065

0.1;B

0.1;B

C1066

0.1;B

C1058

0.1;B

C1057

0.1;B

C1067

10K;1/16J

R1008

VDD3

4.7;B

1608

C1047

4.7;B

1608

C1048

4.7;B

1608

C1005

1K;1/16J

R1033

EV2MA

QEV2MA------N

16.0X16.0

H=1.39

IC101

B2

DQB7

A26

DQB6

A28

DQB5

D25

DQB4

D23

DQB3

B28

DQB2

D26

DQB1

A27

DQB0

E29

DQMA3

J30

DQMA2

R27

DQMA1

W27

DQMA0

A16

DQMB3

A18

DQMB2

B23

DQMB1

B26

DQMB0

F30

DQSA3

J27

DQSA2

T27

DQSA1

V29

DQSA0

D14

DQSB3

D16

DQSB2

A24

DQSB1

D27

DQSB0

G17

DGATEO1

M24

DGATEO0

E21

DGATEI1

N24

DGATEI0

H9

TRACECLK

H8

TRACESYNC

H12

PIPESTAT2

H11

PIPESTAT1

H10

PIPESTAT0

G13

TRACEPKT3

G12

TRACEPKT2

G11

TRACEPKT1

G10

TRACEPKT0

H13

TRSEL

M13

TCK

M11

RTCK

M12

TRST

L11

TMS

L13

TDI

L12

TDO

K8

TSEL1

K7

TSEL0

B12

ZCS

A12

ZRE

G9

ZWE

D5

D15

D4

D14

B5

D13

D6

D12

B4

D11

E4

D10

A6

D9

E6

D8

B3

D7

B6

D6

D7

D5

A5

D4

A4

D3

A3

D2

E5

D1

E7

D0

G4

GPIOA36

G1

GPIOA35

H5

GPIOA34

F1

GPIOA33

E2

GPIOA32

E1

GPIOA31

G5

GPIOA30

G2

GPIOA29

D2

GPIOA28

F2

GPIOA27

F4

GPIOA26

D1

GPIOA25

F5

GPIOA24

B11

GPIOA23

A11

GPIOA22

D10

GPIOA21

D12

GPIOA20

D9

GPIOA19

D11

GPIOA18

A10

GPIOA17

B9

GPIOA16

B8

GPIOA15

D8

GPIOA14

E9

GPIOA13

E8

GPIOA12

E10

GPIOA11

B10

GPIOA10

B7

GPIOA9

A9

GPIOA8

A8

GPIOA7

E12

GPIOA6

A7

GPIOA5

E11

GPIOA4

G8

GPIOA3

H7

GPIOA2

C2

GPIOA1

C1

GPIOA0

N13

VDD_CORE

N14

VDD_CORE

N15

VDD_CORE

N16

VDD_CORE

N17

VDD_CORE

N18

VDD_CORE

P13

VDD_CORE

P18

VDD_CORE

R13

VDD_CORE

R18

VDD_CORE

T13

VDD_CORE

T19

VDD_CORE

U13

VDD_CORE

U19

VDD_CORE

V13

VDD_CORE

V20

VDD_CORE

W13

VDD_CORE

W20

VDD_CORE

Y13

VDD_CORE

Y20

VDD_CORE

AC13

VDD_CORE

AD12

VDD_CORE

AD13

VDD_CORE

AD14

VDD_CORE

AD15

VDD_CORE

AD16

VDD_CORE

AD17

VDD_CORE

AD18

VDD_CORE

H23

VDD_DDR1

H24

VDD_DDR1

J23

VDD_DDR1

J24

VDD_DDR1

K24

VDD_DDR1

R23

VDD_DDR1

R24 VDD_DDR1

T23 VDD_DDR1

T24 VDD_DDR1

G14 VDD_DDR2

G15 VDD_DDR2

G21 VDD_DDR2

G22 VDD_DDR2

G23 VDD_DDR2

H14 VDD_DDR2

H15 VDD_DDR2

H21 VDD_DDR2

M20 VDD_DDRC1

N19 VDD_DDRC1

N20 VDD_DDRC1

P20 VDD_DDRC1

R20 VDD_DDRC1

L18 VDD_DDRC2

L19 VDD_DDRC2

L20 VDD_DDRC2

M18 VDD_DDRC2

M19 VDD_DDRC2

N12 VDD_IO1

P12 VDD_IO1

R11 VDD_IO1

R12 VDD_IO1

T11 VDD_IO1

T12 VDD_IO1

U11 VDD_IO2

U12 VDD_IO2

V11 VDD_IO3

V12 VDD_IO4

W11 VDD_IO4

Y11 VDD_IO5

Y12 VDD_IO5

AC8 VDD_IO5

AC9 VDD_IO5

AD8 VDD_IO5

AB23 VDD_IO6

AC19 VDD_IO6

AC20 VDD_IO6

AC21 VDD_IO6

AC22 VDD_IO6

AD20 VDD_IO6

AD21 VDD_IO6

E13 VDD_IO7

N11 VDD_IO7

P11 VDD_IO7

H22 VDD_IOA

AC10 VDD_IOB

AD9 VDD_IOB

A1

GND

A2

GND

A29 GND

A30 GND

B1

GND

B2

GND

B29 GND

B30 GND

C29 GND

C30 GND

D13 GND

E14 GND

P14 GND

P15 GND

P16 GND

P17 GND

R14 GND

R15 GND

R16 GND

R17 GND

T14 GND

T15 GND

T16 GND

T17 GND

T18 GND

U14 GND

U15 GND

U16 GND

U17 GND

U18 GND

V14 GND

V15 GND

V16 GND

V17 GND

V18 GND

VDD1.8

10K

RB101

12

10K

RB101

34

10K

RB101

56

10K

RB101

78

10K;1/16J

R1004

VDD3

LCDAN

20

1AV4J10JR200G

CN105

4

ZCHGDONE

5

CHG

1

AL3.2V

2

AL3.2V

3

AL3.2V

AL3.2V

MICR

LCDCA

MICL

ZCHGDONE

ST_CHG

0.1;B C1774

31

1AV4J11VR311G

CN103

10

LCD_AN

4

MIC_R+

11

LCD_CA

5

A_GND

12

LCDSD

6

A_GND

13

LCDCK

7

GND

14

LCDEN

8

MR_PANEL_TURN

15

LCDRESET

9

VDD3

16

VD

17

HD

18

GND

19

LMCLK

20

GND

1

GND

2

GND

3

MIC_L+

21

LCDD7

22

LCDD6

23

LCDD5

24

LCDD4

25

LCDD3

26

LCDD2

27

LCDD1

28

LCDD0

29

VDD3

30

GND

31

GND

Z1

Z2

AA_GND

TDI

D13

A8

D15

A12

D2

A14

TMS

D14

A15

D10

A4

D3

TRST

D1

D5

D7

D8

DGATE0

D12

A7

D0

D9

A6

D6

TDO

FLCTL

A11

D11

TCK

ZFRD

ZFWR

A1

A3

A2

D4

A9

A10

A5

TMODE

TSEL

RTCK

PAON1

PAON2

ZVMUTE

A16

A13

INT_ONENAND

DQSA0

DQSA1

DQSA2

DQSA3

DQMA0

DQMA1

DQMA2

DQMA3

ZCS0

LCDHD

LCDVD

MR_PANELTURN

FLCTL

ST_CHG

ZCHGDONE

LCDD4

LCDD3

LCDD2

LCDD1

LCDD0_ZBOOT

LCDD5

LCDD6

LCDD7

LMCLK

LCDRESET

LCDSD

LCDCK

LCDEN

LCDRESET

TO ST1 CN541

TO VF1 CN172

1.0

1.8

3.3