CQ7-A30

CQ7-A30 - Rev. First Edition: 1.0 - Last Edition: 2.0 - Author: S.B. - Reviewed by G.G. Copyright © 2016 SECO S.r.l.

51

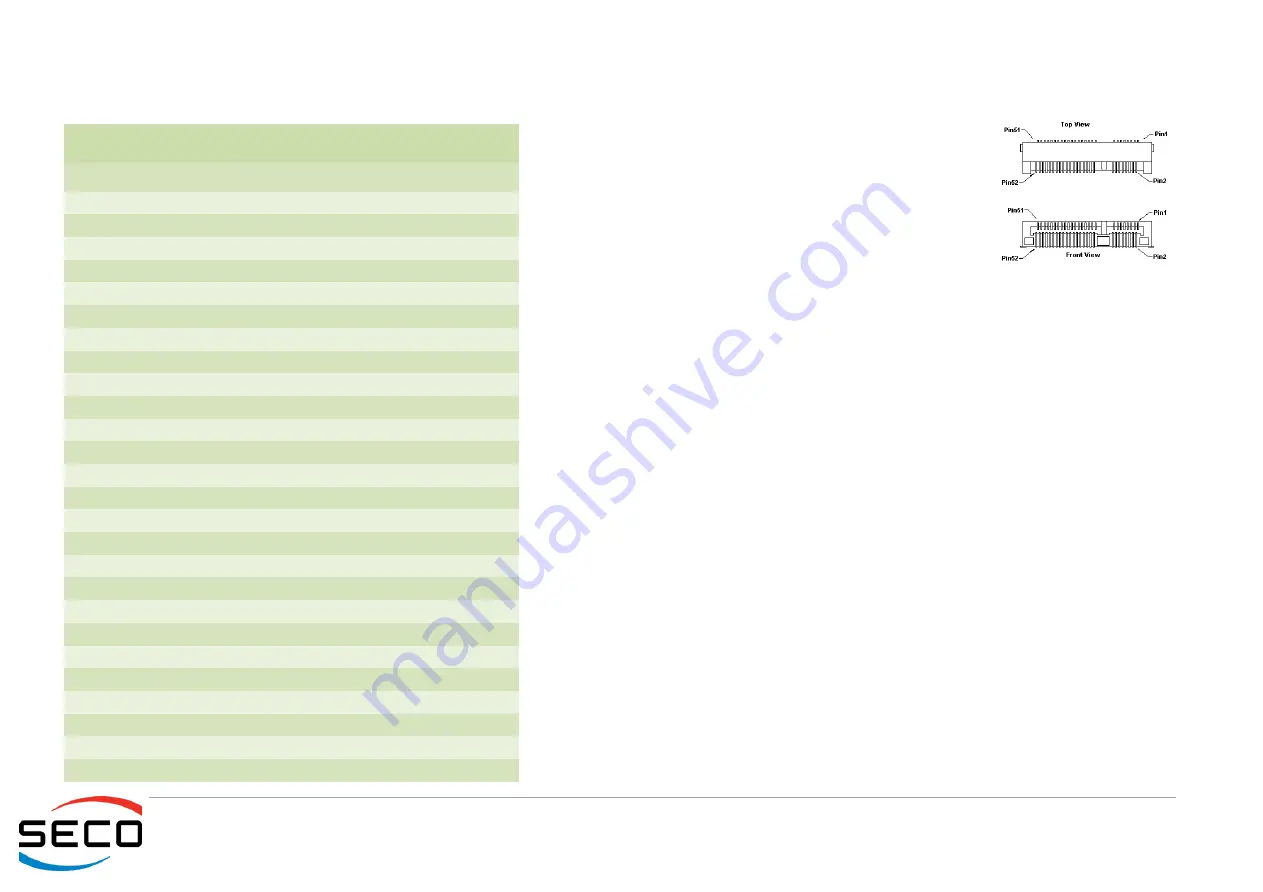

3.3.13

miniPCI-express slot

To add communications functionality, or other features not

already available, it is possible to use Half-/ Full-size mini-PCI

Express cards, using the dedicate connector, CN18, which is a

standard 52pin miniPCI Express connector, type LOTES AAA-

PCI-047-K01 or equivalent, H=9.0mm, with the pinout shown in

the table on the left.

CQ7-A30 carrier board allows inserting both Half-mini and Full-

mini PCI express cards. Support for both form factors is ensured

by the possibility, for the customer, of moving the mechanical latch in the position necessary

to support Half-miniPCI-e cards or Full-miniPCI-e cards.

On the slot are also available the signals for interfacing to miniSIM cards, so that it is possible

to use miniPCI Express modems.

As explained in the previous paragraph, PCI-e lane is available on CN18 when jumper JP1 is

not inserted, otherwise PCI-e lane #0 would be routed to PCI-e x16 slot CN14.

Signals carried to miniPCI-express slot are the following:

P/PCIE0_TX-: PCI Express lane #0, Transmitting Output Differential pair.

P/PCIE0_RX-: PCI Express lane #0, Receiving Input Differential pair.

mP / mPCIE_CLK-: Reference Clock for miniPCI express slot, Differential Pair.

PCIE_WAKE#: Board

’

s Wake Input, it must be externally driven by the miniPCI-e module

inserted in the slot when it requires waking up the system.

mPCIE_RST#: Reset Signal derived from those sent from Qseven

®

module to all devices

available on the board. It is a 3.3V active-low signal.

mPCIE_CLOCK_REQUEST# PCI Express Clock Request Input. This signal shall be driven

correctly by any module inserted in the miniPCI express slot, in order to ensure that the PCI-e

clock buffer available on the carrier board makes available the reference clock for the miniPCI-

e slot.

SMB_CLK: SM Bus control clock line for System Management, managed by the Qseven

®

module.

SMB_DATA: SM Bus control data line for System Management, managed by the Qseven

®

miniPCI-e Slot - CN18

Pin Signal

Pin Signal

1

PCIE_WAKE#

2

+3.3V_A

3

N.C.

4

GND

5

N.C.

6

+1.5V_S

7

mPCIE_CLOCK_REQUEST#

8

UIM_PWR

9

GND

10

UIM_DATA

11

mPCIE_CLK-

12

UIM_CLK

13

mP

14

UIM_RESET

15

GND

16

UIM_SPU

17

N.C.

18

GND

19

N.C.

20

W_DISABLE#

21

GND

22

mPCIE_RST#

23

PCIE0_RX-

24

+3.3V_A

25

P

26

GND

27

GND

28

+1.5V_S

29

GND

30

SMB_CLK

31

PCIE0_TX-

32

SMB_DAT

33

P

34

GND

35

GND

36

USB_mPCIE-

37

GND

38

US

39

+3.3V_A

40

GND

41

+3.3V_A

42

LED_WWAN0#

43

GND

44

LED_WLAN0#

45

N.C.

46

LED_WPAN0#

47

N.C.

48

+1.5V_S

49

N.C.

50

GND

51

N.C.

52

+3.3V_A