8

AK - 45

CHASSIS

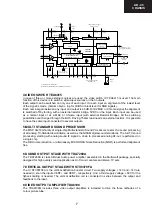

9.POWER SUPPLY (SMPS)

The DC voltages required at various parts of the chassis are provided by an SMPS transformer

controlled by the IC MC44608, which is designed for driving, controlling and protecting switching

transistor

of

SMPS. The

transformer

generates

145V for

Horizontal output stage

, +/-14V for audio

amplifier, 5V and

3.3V stand by voltage and 8V, 12V and 5V supplies for other different parts of the chassis.

An optocoupler is used to control the regulation of line voltage and stand-by power consumption. There

is a regulation circuit in secondary side. This circuit produces a control voltage according to the

changes in 145V DC voltage, via an optocoupler (TCET1102G) to pin3 of the IC.

During the switch on period of the transistor, energy is stored in the transformer. During the switch off

period energy is fed to the load via secondary winding. By varying switch-on time of the power

transistor, it

controls

each

portion

of

energy

transferred

to the second

ary

side such that the output

voltage level

remains nearly independent of load variations.

10.MICROCONTROLLER SDA55XX

10.1.General Features

• Feature selection via special function register

• Simultaneous reception of TTX, VPS, PDC, and WSS (line 23)

• Supply Voltage 2.5 and 3.3 V

• ROM version package PSDIP52-2, PMQFP64-1

• Romless version package PMQFP100-2, PLCC84-2

10.2.External Crystal and Programmable Clock Speed

• Single external 6MHz crystal, all necessary clocks are generated internally

• CPU clock speed selectable via special function registers.

• Normal Mode 33.33 MHz CPU clock, Power Save mode 8.33 MHz

10.3.Microcontroller Features

• 8bit 8051 instruction set compatible CPU.

• 33.33-MHz internal clock (max.)

• 0.360 ms (min.) instruction cycle

• Two 16-bit timers

• Watchdog timer

• Capture compare timer for infrared remote control decoding

• Pulse width modulation unit (2 channels 14 bit, 6 channels 8 bit)

• ADC (4 channels, 8 bit)

• UART (rxd, txd)

10.4.Memory

• Non-multiplexed 8-bit data and 16 … 20-bit address bus (ROMless Version)

• Memory banking up to 1Mbyte (Romless version)

• Up to 128 Kilobyte on Chip Program ROM

• Eight 16-bit data pointer registers (DPTR)

• 256-bytes on-chip Processor Internal RAM (IRAM)

• 128bytes extended stack memory.

• Display RAM and TXT/VPS/PDC/WSS-Acquisition-Buffer directly accessible via MOVX

• UP to 16KByte on Chip Extended RAM (XRAM) consisting of;

- 1 Kilobyte on-chip ACQ-buffer-RAM (access via MOVX)

- 1 Kilobyte on-chip extended-RAM (XRAM, access via MOVX) for user software

- 3 Kilobyte Display Memory

10.5.Display Features

• ROM Character Set Supports all East and West European Languages in single device

• Mosaic Graphic Character Set

• Parallel Display Attributes

• Single/Double Width/Height of Characters

• Variable Flash Rate

• Programmable Screen Size (25 Rows x 33...64 Columns)

• Flexible Character Matrixes (HxV) 12 x 9...16

• Up to 256 Dynamical Redefinable Characters in standard mode; 1024 Dynamical Redefinable

Characters in Enhanced Mode

• CLUT with up to 4096 colour combinations

Summary of Contents for C-2890EES

Page 7: ...7 C 2890EES CHASSIS LAYOUT Mother Unit CRT Unit Control Panel Unit ...

Page 69: ...53 AK 45 CHASSIS 14 6 GEOMETRY ADJUSTMENT 4 3 FORMATS 4 3 MODE 16 9 MODE ...

Page 70: ...54 AK 45 CHASSIS 16 9 FORMATS AUTO MODE ...

Page 71: ...55 AK 45 CHASSIS REGULAR MODE ...

Page 72: ...56 AK 45 CHASSIS ZOOM 14 9 MODE ...

Page 73: ...57 AK 45 CHASSIS ZOOM 16 9 MODE ...

Page 74: ...58 AK 45 CHASSIS SUBTITLE ZOOM MODE ...

Page 75: ...59 AK 45 CHASSIS FULL MODE ...

Page 76: ...60 AK 45 CHASSIS PANORAMIC MODE ...

Page 86: ...70 AK 45 CHASSIS 1 I H G F E D C B A 2 3 4 5 6 7 16 7 Schematic Diagram of CRT Socket Circuit ...

Page 91: ...75 AK 45 CHASSIS Notes ...