– 57 –

CD-DD4500

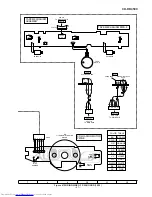

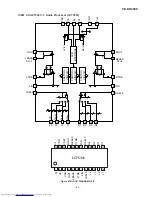

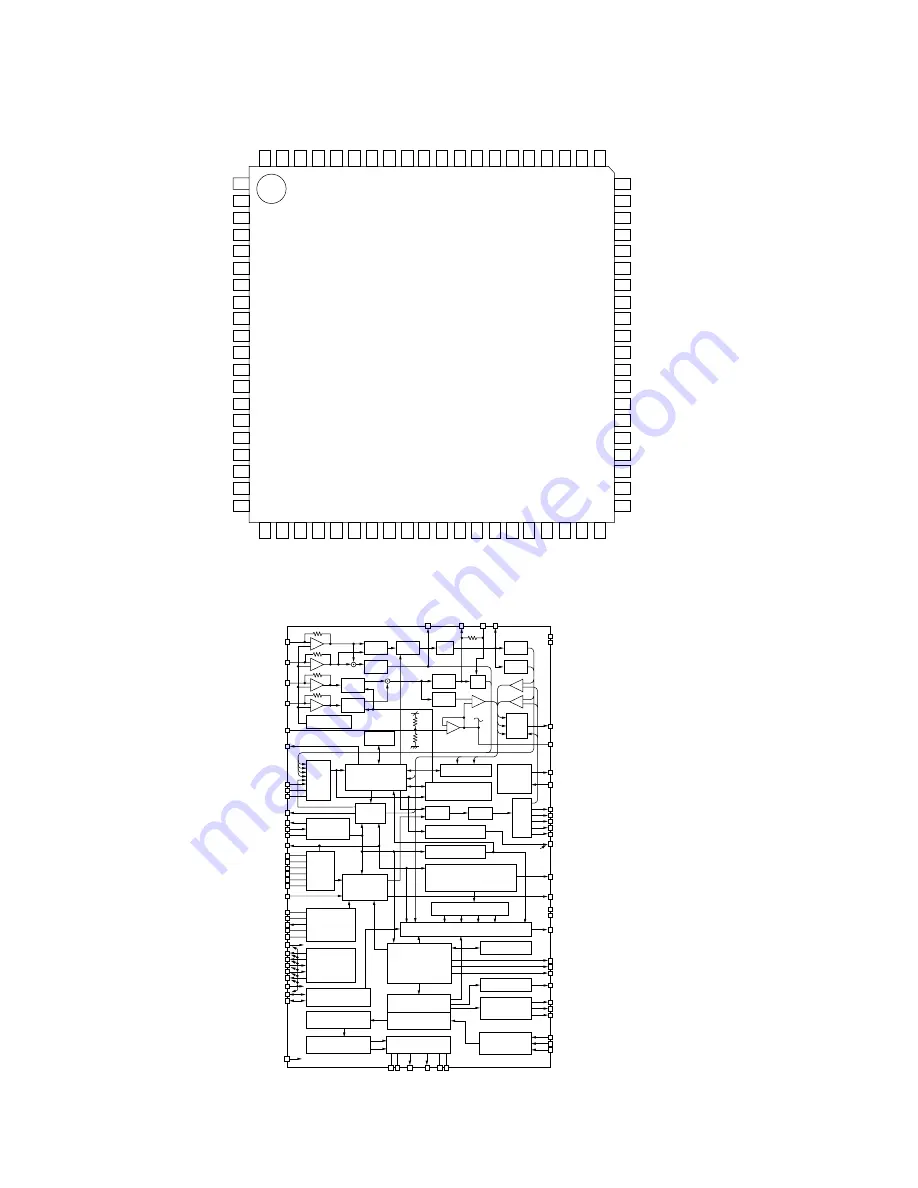

Figure 57 BLOCK DIAGRAM OF IC

IC1 VHiLC78645NE1: CD Servo (LC78645NE)

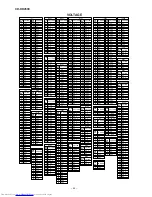

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35 36

37

38

39

40

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66 65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

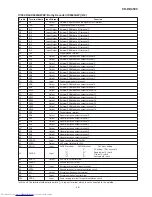

SLC0

SLCIST

EFMIN

RF

RFVDD

RFVSS

FIN1

FIN2

TIN1

TIN2

VREF

REFI

FE

TEC

TE

RFMON

JITTC

ADAVDD

ADAVSS

TD0

FD0

SPD0

SLD0

GPDAC

CONT4

CONT5

SBCK/CONT6

SBCK/FG

DEFECT

V/*P

FSEQ

MONI1

MONI2

MONI3

MONI4

MONI5

(3.3V)VSS

VDD

DOUT

TEST

LDD

LDS

FR

VVDD

PCKIST

VVSS

PD02

PD01

CONT1

CONT2

CONT3

VSS

VDD5

DRF

*RES

*WRQ

DO

DI

CL

CE

DATA

DATACK

LRSY

ASDFIN

ASDACK

ASLRCK

16MOUT

EFLG

C2F

XVSS

FSX/16MIN

XIN

XOUT

XVDD

RVDD

RCH0

RVSS

LVSS

LCH0

LVDD

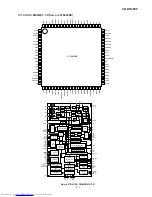

LC78645NE

+

–

+

–

+

–

+

–

–

–

+

+

MIX

LPF

LPF

LPF

TBAL

TBAL

RAM

LEVEL SET

AGC

EQ

SW

PH

BH

+

–

+

–

+

–

+

–

MONI

CONT

A/D

SERVO PROCESSOR

TRACK JUMP

AUTO ADJUST

JITTER

DETECT

1bit DAC

8FS

DIGITAL FILTER

GENERAL-PURPOSE

PORTS

COMMAND

INTERFACE

CLOCK

GENERATOR

CLV,CAV

CONTROL

PLL

VCEC

SLICE LEVEL

CONTROL

APC

S/H

D/A

SW

DRF

RUPTURE DEFECT

FRAME SYNC

DETECT,PROTECT INSERT,

EFN DECODE

VDD

SUBCODE DECODE CRC

MONITOR SIGNAL SELECTOR

RAM

ERROR

CORRECTION

AUDIO CD

AUDIO OUT

SERIAL

OUT

EXTERNAL

AUDIO IN

INTERPOLATION

MUTE

ATTENUATION

DEEMPHSIS

LPF

FIN1

FIN2

TIN1

TIN2

REF1

DETECT

ADIN

ADAVDD

ADAVSS

JITTC

SLC0

EFMIN

SLCIST

PCK

PDO1

PDO2

FR

PCKIST

VVDD

VVSS

SBCK/FG

XIN

XOUT

16MOUT

XVDD

XVSS

*RES

*WRQ

CL

CE

DI

DO

VDD5V

CONT1, 2, 3

TEST

CONT4, 5

SBCK/CONT6

LVDD

LVSS

LCHO

RCHO

RVDD

RVSS

ASDFIN

ASDQCK

ASLRCK

DATA

DATACK

LRSY

DOUT

EFLG

C2F

FSK/16MIN

MONI1~5

VSS

VDD

V/*P

FSEQ

DRF

GPDAC

SPD0

SLD0

TD0

FD0

LDS

LDD

VREF

RFMON

RFVSS

RFVDD

RF

TEC

TE

FE

Summary of Contents for CD-DD4500

Page 70: ...CD DD4500 70 MEMO ...

Page 87: ...CD DD4500 16 MEMO ...