XL-30H/30W

– 50 –

83

DVDD

—

D/A converting section power terminal.

84

DVR

—

Reference voltage terminal.

85

LO

Output

L channel data forward rotation output terminal.

86

DVSL

—

L channel D/A converting section power terminal.

87*

TEST1

Input

Test mode terminal. To be opened usually.

88*

TEST2

Input

Test mode terminal. To be opened usually.

89*

TEST3

Input

Test mode terminal. To be opened usually.

90-93

BUS0-BUS3

Input/Output

Microcomputer interface data input/output terminal.

94

VDD

—

D power terminal.

95

VSS

—

Digital ground terminal.

96

BUCK

Input

Microcomputer interface clock input terminal.

97

/CCE

Input

Microcomputer interface chip enable signal input terminal. "L": BUS0 to 3 is active.

98*

TEST4

Input

Test mode terminal. To be opened usually.

99*

/TSMOD

Input

Local test mode selection terminal.

100

/RST

Input

Reset signal input terminal. "L": Reset.

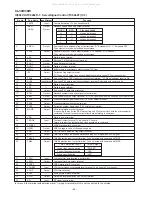

IC802 VHiTC9462F/-1: Servo/Signal Control (TC9462F) (3/3)

Pin No.

Port Name

Function

Input/Output

In this unit, the terminal with asterisk mark (*) is (open) terminal which is not connected to the outside.

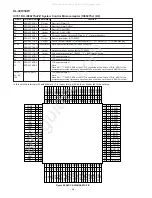

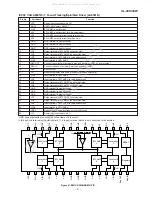

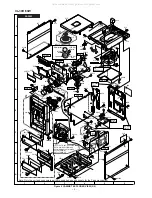

Figure 50 BLOCK DIAGRAM OF IC

2

3

4

5

1

7

8

9

6

12

13

14

15

11

17

18

19

10

16

22

23

24

25

21

27

28

29

20

30

26

42

43

44

45

41

47

48

49

50

46

32

33

34

35

31

37

38

39

40

36

89

88

87

86

90

84

83

82

81

85

99

98

97

96

100

94

93

92

91

95

72

73

74

75

71

77

78

79

70

80

76

62

63

64

65

61

67

68

69

60

66

52

53

54

55

51

57

58

59

56

LPF

1Bit

DAC

Microcomputer

interface

Correction

circuit

Audio output

circuit

Digital

out

16KRAM

Sub-code

demodulation

circuit

Status

PLL

TMAX

VCO

Data

slicer

CLV

servo

D/A

PWM

Servo control

ROM

RAM

Digital equalizer

adjustment circuit

Address

circuit

Clock

generator

/RST

/TSMOD

TEST4

/CCE

BUCK

VSS

VDD

BUS3

BUS2

BUS1

BUS0

TEST3

TEST2

TEST1

DVSL

LO

DVR

DVDD

RO

DVSR

LPFN

LPFO

PVREF

VCOREF

VCOF

AVSS

SLCO

RFI

AVDD

RFCT

RFZI

RFRP

FEI

SBAD

TSIN

TEI

TEZI

FOO

TRO

VREF

TMAX

TMAXS

PDO

ZDET

HSSW

P2VREF

TESIO0

VDD

MONIT

COFS

SPDA

SPCK

SBSY

SFSY

DATA

VSS

VDD

CLCK

SBOK

IPF

MBOV

DOUT

AOUT

BCK

VSS

LRCK

EMPH

/UHSO

/HSO

TEST0

RFGC

TEBC

FMO

FVO

DMO

2VREF

SEL

FLGA

FLGB

FLGC

FLGD

VDD

VSS

IO0

IO1

IO2

IO3

/DMOUT

/CKSE

/DACT

TESIN

TESIO1

VSS

PXI

PXO

VDD

XVSS

XI

XO

XVDD

Synchronizing

signal guarantee

EFM demodulation

A/D

All manuals and user guides at all-guides.com