DV-L70S

DV-L70BL

DV-L70W

32

35

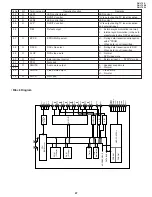

CLK

System Clock

Active on the positive going edge to sample all inputs.

18

CS

Chip Select

Disables or enables device operation by masking or enabling all inputs

except CLK. CKE and L(U)DQM

34

CKE

Clock Enable

Masks system clock to freeze operation from the next clock cycle.

CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in stanby.

21~24

A0~A10/AP

Address

Row/column address are multiplexed on the same pins.

27~32

Row address: RA0~RA10, column address: CA0~CA7

20

19

BA

Bank Select Address

Selects bank to be activated during row address latch time.

Selects bank for read/write during clumn address latch time.

17

RAS

Row Address Strobe

Latches row address on the positive going edge of the CLK with RAS low.

Enables row access & precharge.

16

CAS

Column Address Strobe

Latches addresses on the positive going edge of the CLK with CAS low.

Enables row access.

15

WE

Write Enable

Enable write operation and row precharge.

Latches data in starting from CAS, WE active.

14, 36

DOML(U)

Data Input/Output Mask

Makes data output Hi-Z, tsHZ after the clock and masks the output.

Blocks data input when L(U)DQM active.

2, 3, 5,

DQ0~15

Data Input/Output

Data inputs/outputs are multiplexed on the same pins.

6, 8, 9, 11, 12, 39, 40,

42, 43, 45, 46, 48, 49

Vcc/Vss

Power Supply/Ground

Power and ground for the input buffers and the core logic.

25, 1/26, 50

Vcc/VssO

Data Output Power/Ground Isolated power supply and ground for the output buffers to provide

44, 38, 13, 7/4, 10, 41, 47

improved noise immunity.

33, 37

NC/RFU

No Connection/

This pin is recommanded to be left No Connection on the device

Reserved for Future Use

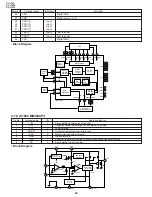

9-10. IC602 IX0750TA

Terminal

Terminal Name

Name

Input Function

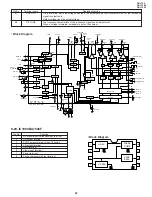

• Block Diagram

Self Refresh Counter

Refresh

Counter

Refresh

Interval Timer

Precharge

Row Active

Column Active

Address

Register

Burst Length

Counter

Overflow

Column Addr.

Latch & Counter

Column Decoder

Sense AMP & I/O gates

Column Decoder

Sense AMP & I/O gates

512K x 16

Bank 1

512K x 16

Bank 0

Row Addr. Latch/Predecode

Data Input/Output Buffers

Row Addr. Latch/Predecode

Row Decoder

Ref. Addr.[0:11]

Auto/Self Refresh

State Machine

Test Mode

Mode Register

I/O Control

Address[0:10]

CLK

CKE

BA(A11)

CS

RAS

CAS

WE

UDQM

LDQM

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

Summary of Contents for DV-L70BL

Page 2: ...DV L70S DV L70BL DV L70W 2 1 IMPORTANT SAFEGUARDS AND PRECAUTIONS ...

Page 6: ...DV L70S DV L70BL DV L70W 6 For details on the use of each control 4 PART NAMES ...

Page 53: ...53 DV L70S DV L70BL DV L70W 11 WIRING DIAGRAM ...

Page 82: ...Ref No Part No Description Code Ref No Part No Description Code 95 DV L70S DV L70BL DV L70W ...