DX-SX1H

– 59 –

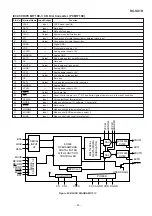

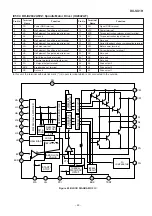

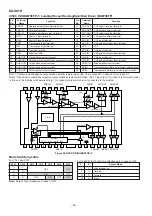

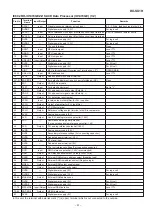

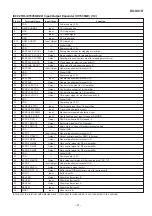

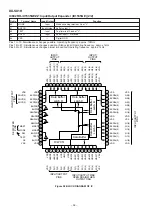

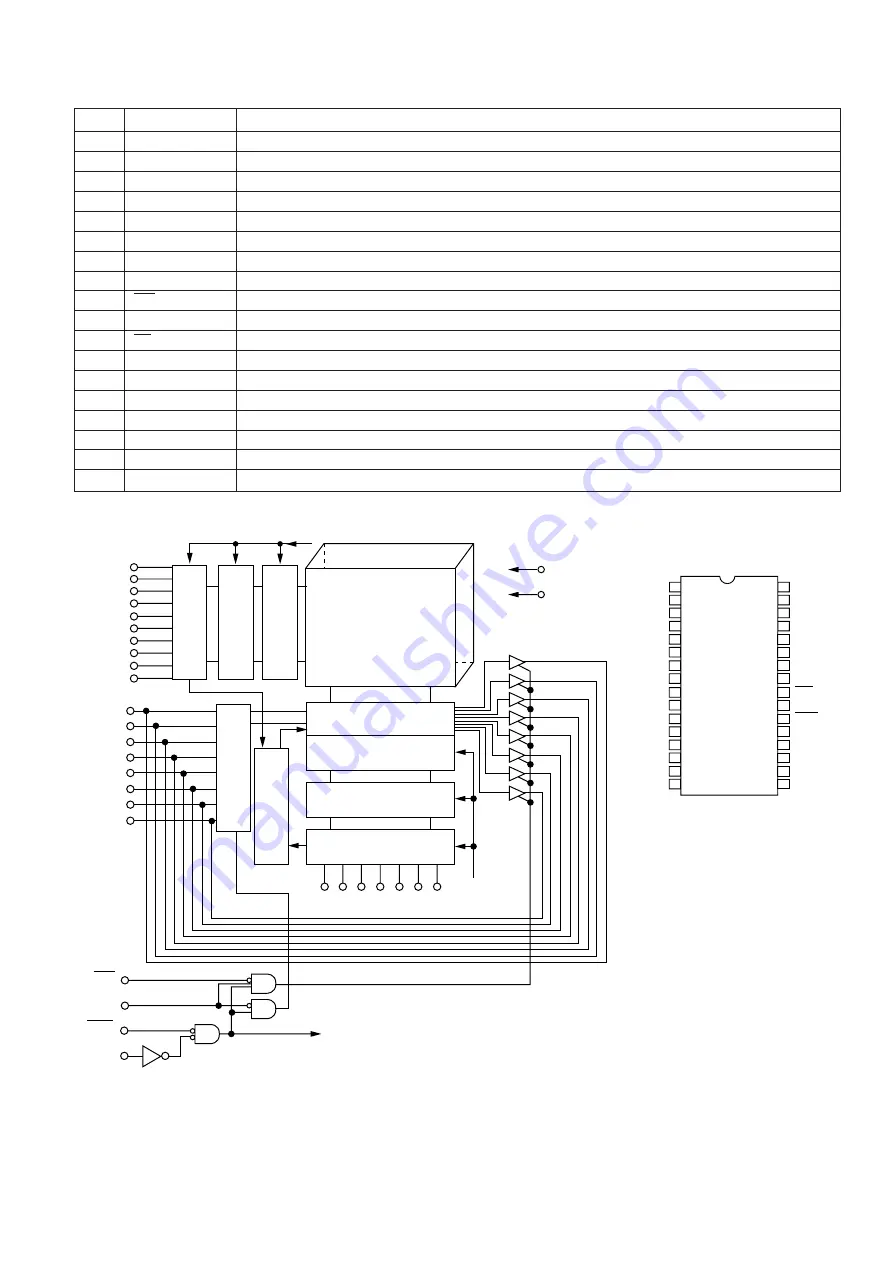

IC804 RH-iX2839AFZZ: 1Mbit SRAM (IX2839AF)

1*

NC

Not used

2

A16

Address input

3

A14

Address input

4

A12

Address input

5-12

A7-A0

Address input

13-15

I/O1-I/O3

Data input/output

16

GND

Ground

17-21

I/O4-I/O8

Data input/output

22

CE1

Chip enable input

23

A10

Address input

24

OE

Output enable input

25

A11

Address input

26, 27

A9, A8

Address input

28

A13

Address input

29

R/W

Read/Write input

30

CE2

Chip enable input

31

A15

Address input

32

VDD

Power terminal (+5V)

Pin No.

Terminal Name

In this unit, the terminal with asterisk mark (*) is (open) terminal which is not connected to the outside.

Function

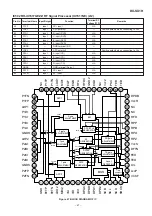

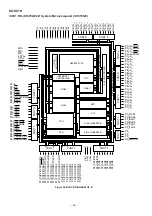

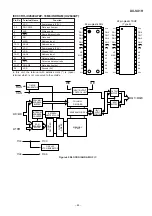

A4

CE

A5

A6

A7

A8

A12

A13

A14

A15

A16

I/O1

I/O8

OE

R/W

CE1

CE2

MEMORY CELL

ARRAY

1024 x 28 x 8

(1048576)

VDD

GND

~

CE

A0

A1

A2

A3

A9

A10

A11

CE

ROW ADDRESS

BUFFER

ROW ADDRESS

REGISTER

ROW ADDRESS

DECODER

DATA CONTROL

CLOCK

GENERATOR

SENSE AMPLIFIER

COLUMN ADDRESS

DECODER

COLUMN ADDRESS

REGISTER

COLUMN ADDRESS

BUFFER

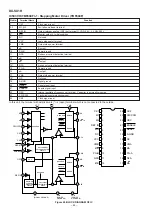

(TOP VIEW)

N.C.

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O1

I/O2

I/O3

GND

VDD

A15

CE2

R/W

A13

A8

A9

A11

OE

A10

CE1

I/O8

I/O7

I/O6

I/O5

I/O4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

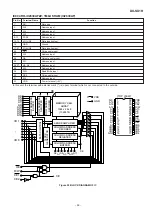

Figure 59 BLOCK DIAGRAM OF IC