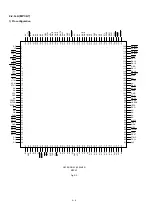

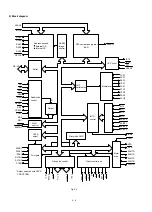

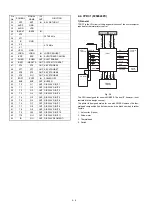

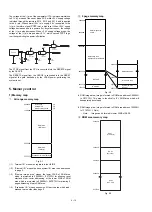

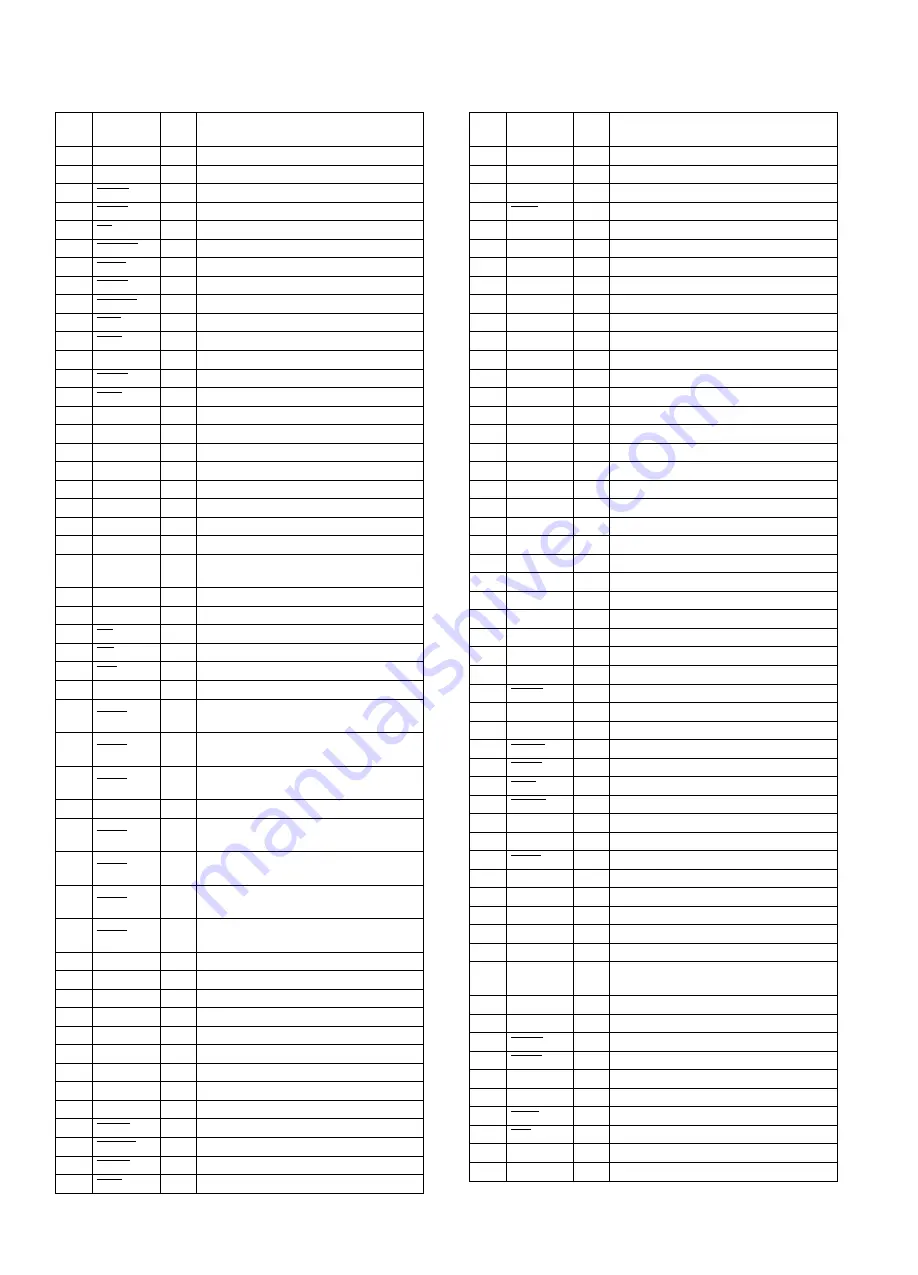

3) Pin description

Pin

No.

Signal

name

In/

Out

Function

1

RF

Out

Receipt side paper feed solenoid (NU)

2

JF

Out

Journal side paper feed solenoid (NU)

3

PCUT

Out

Printer partial cut signal (NU)

4

FCUT

Out

Printer auto cut signal (NU)

5

VF

Out

Multi line validation paper feed (NU)

6

STAMP

Out

Printer stamp signal (NU)

7

SLFS

Out

Slip printer paper feed singnal (NU)

8

SLRS

Out

Slip printer release signal (NU)

9

SLMTD

Out

Slip printer motor drive signal (NU)

10

RES

Out

Peripheral output reset

11

TRG

Out

Dot head trigger signal (NU)

12

TRG

Out

Dot head trigger signal (NU)

13

POFF

In

Power off signal input

14

INT1

In

(NU)

15

HTS1

Out

8 bit serial port output (for CKDC8)

16

SCK1

Out

Serial port shift clock output (for CKDC8)

17

STH1

In

8 bit serial port input (for CKDC8)

18

RAS VZ

—

Chip select (NU)

19

—

—

Nu

20

VCC

—

+5V

21

GND

—

GND

22

INTMCR

—

Interrupt (NU)

23

VRESC

Out

Turns active when reset and power down

is met

24

SLTMG

In

Slip printer timing signal (NU)

25

SLRST

In

Slip printer reset signal (NU)

26

AS

In

Address strobe

27

RD

In

Read strobe

28

WR

In

Write strobe

29

f

In

(

f

) System clock (9.83 MHz)

30

SDT7

Out

Slip printer printhead drive signal (dot7)

(NU)

31

SDT6

Out

Slip printer printhead drive signal (dot6)

(NU)

32

SDT5

Out

Slip printer printhead drive signal (dot5)

(NU)

33

GND

—

GND

34

SDT4

Out

Slip printer printhead drive signal (dot4)

(NU)

35

SDT3

Out

Slip printer printhead drive signal (dot3)

(NU)

36

SDT2

Out

Slip printer printhead drive signal (dot2)

(NU)

37

SDT1

Out

Slip printer printhead drive signal (dot1)

(NU)

38

D0

I/O

Data bus 0

39

D1

I/O

Data bus 1

40

D2

I/O

Data bus 2

41

D3

I/O

Data bus 3

42

GND

—

GND

43

D4

I/O

Data bus 4

44

D5

I/O

Data bus 5

45

D6

I/O

Data bus 6

46

D7

I/O

Data bus 7

47

SPRQ

Out

SSP interrupt request to CPU

48

RESET

In

MPCA reset

49

SHEN

In

Shift enable from CKDC8

50

INT3

In

Interrupt signal (Nu)

Pin

No.

Signal

name

In/

Out

Function

51

RXD2

Out

8 bit serial port output to CPU

52

TXD2

In

8 bit serial port input from CPU

53

SCK2

In

Serial port shift clock input from CPU.

54

IRQ0

Out

Interrupt request to CPU

55

A0

In

Address bus 0

56

A1

In

Address bus 1

57

A2

In

Address bus 2

58

A3

In

Address bus 3

59

A4

In

Address bus 4

60

A5

In

Address bus 5

61

GND

—

GND

62

VCC

—

+5V

63

A6

In

Address bus 6

64

A7

In

Address bus 7

65

A8

In

Address bus 8

66

A9

In

Address bus 9

67

A10

In

Address bus 10

68

A11

In

Address bus 11

69

A12

In

Address bus 12

70

A13

In

Address bus 13

71

A14

In

Address bus 14

72

A15

In

Address bus 15

73

A16

In

Address bus 16

74

A17

In

Address bus 17

75

A18

In

Address bus 18

76

A19

In

Address bus 19

77

A20

In

Address bus 20

78

A21

In

Address bus 21

79

A22

In

Address bus 22

80

LCDC

—

LCD CS (NU)

81

A23

In

Address bus 23

82

TRGI

In

Dot pulse control/drive signal (NU: GND)

83

PTMG

Out

Printer timing signal to CPU

84

PRST

Out

Printer reset signal to CPU

85

RDY

In

Ready from FMC unit

86

IPLON

In

To option connector (NU) +5V

87

MD1

In

Mode select input (GND)

88

MD0

In

Mode select input (GND)

89

TEST

In

+5V

90

MA15

—

Image address 15

91

MA18

—

Nu

92

MA19

—

Nu

93

RCVRDY1

—

Nu: +5V

94

RCVRDY2

—

Nu: +5V

95

RC0

—

Remote control encord signal for CPU

(NU)

96

IRTX

—

I/R output for LED (NU)

97

UASCK

—

I/R serial data shift clock (NU)

98

UARX

—

I/R serial data for CPU (NU)

99

UATX

—

I/R serial data from CPU (NU) +5V

100

VCC

—

+5V

101

GND

—

GND

102

IRRX

—

I/R input from I/R unit (NU) +5V

103

RCI

—

I/R input from I/R unit (NU) +5V

104

DAX1

—

System clock (NU)

105

DAX2

—

Nu

4 – 7

Summary of Contents for ER-A450

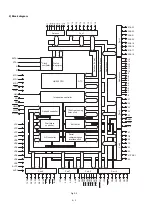

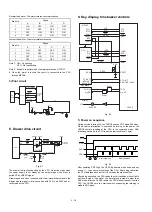

Page 51: ...MAIN PWB LAYOUT 1 SIDE A 8 15 ...

Page 52: ... 2 SIDE B 8 16 ...

Page 53: ...PS PWB FRONT DISPLAY PWB POP UP DISPLAY PWB 8 17 ...