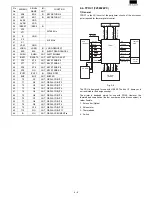

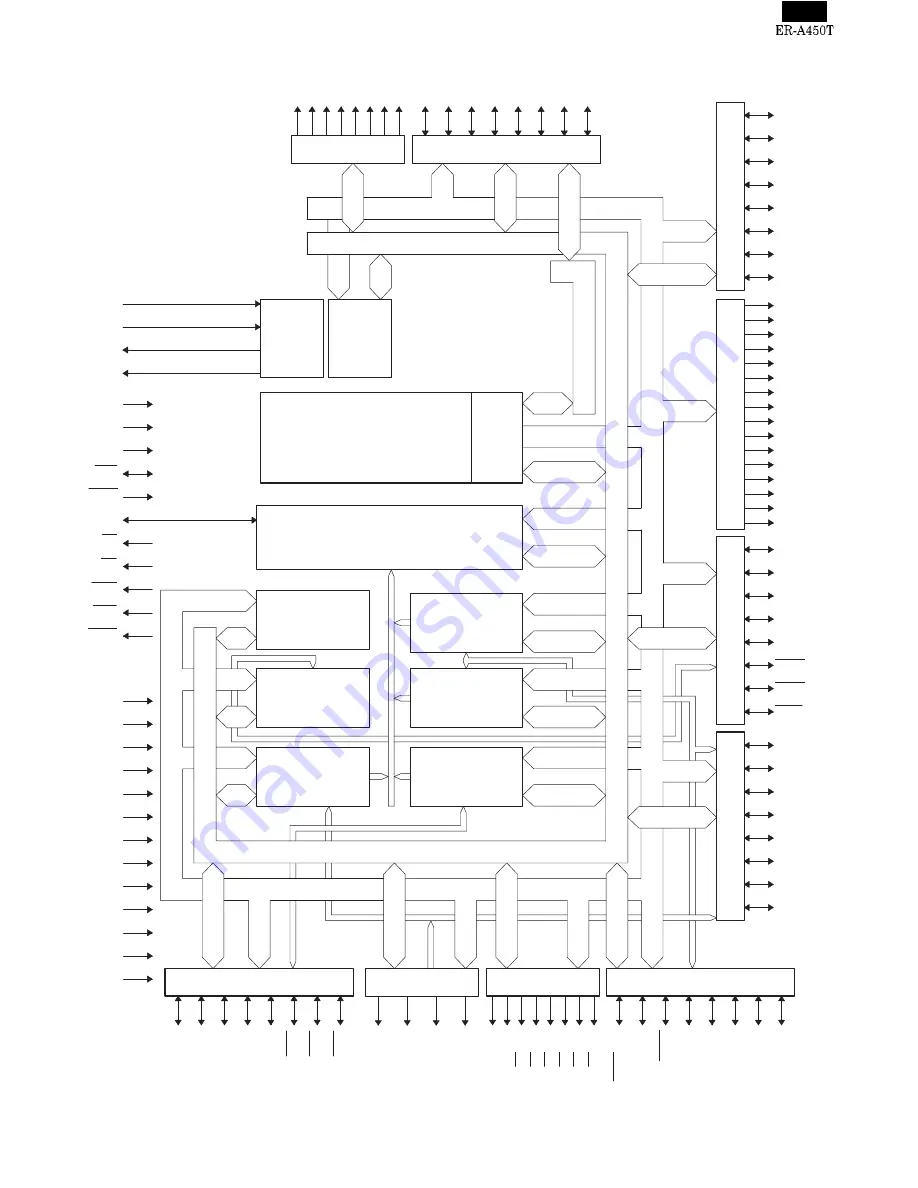

2) Block diagram

Fig. 2-2

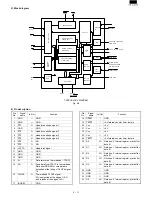

P47

FTI2

P45

FTI1

P43

P42

P41/TMCI

P40

P37

P36

P35

P34

P33

BREQ

BACK

WAIT

P27/A23

P26/A22

P25/A21

P24/A20

P23/A19

P22/A18

P21/A17

P20/A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AVCC

AVSS

MD2

MD1

MD0

RES

STBY

NMI

AS

RD

HWR

LWR

RFSH

EXTAL

XTAL

E

P17

P16

P15

P14

P13

P12

P11

P10

D7

D6

D5

D4

D3

D2

D1

D0

ST

OP/P57

P56

FMRS

P54

P53

P52

P51

P50

P67

P66

RS/P65

RR/P64

CD/P63

CS/P62

DR/P61

ER/P60

P73

AN2

AN1

AN0

TXD2

RXD2

TXD1

RXD1

SCK2

IRQ2

IRQ1

IRQ0

H8/500 CPU

DTC

Serial

communication

interface x 2ch

8bit timer

16bit free running

timer x 2ch

Refresh controller

Wait state

controller

A/D convertor

Interruption controller

Clock

oscillator

Watch

dog timer

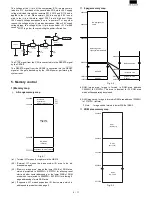

Data bus

Port 1

Dat

a b

u

s (Lo

w

er)

Dat

a b

u

s (U

pper

)

Add

res

s b

u

s

Po

rt

2

Po

rt

3

Po

rt

4

Port 5

Port 6

Port 7

Port 8

Add

res

s b

u

s

X

4 – 3

Summary of Contents for ER-A450T

Page 56: ...2 MAIN PWB LAYOUT 1 SIDE A ...

Page 57: ... 2 SIDE B ...

Page 59: ...4 FRONT DISPLAY PWB LAYOUT 5 POP UP DISPLAY PWB LAYOUT ...

Page 61: ...7 PS PWB LAYOUT ...