LL-T15S3

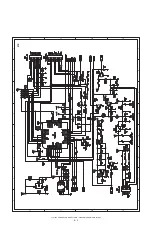

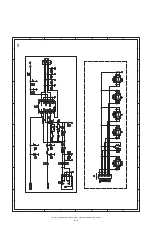

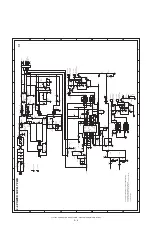

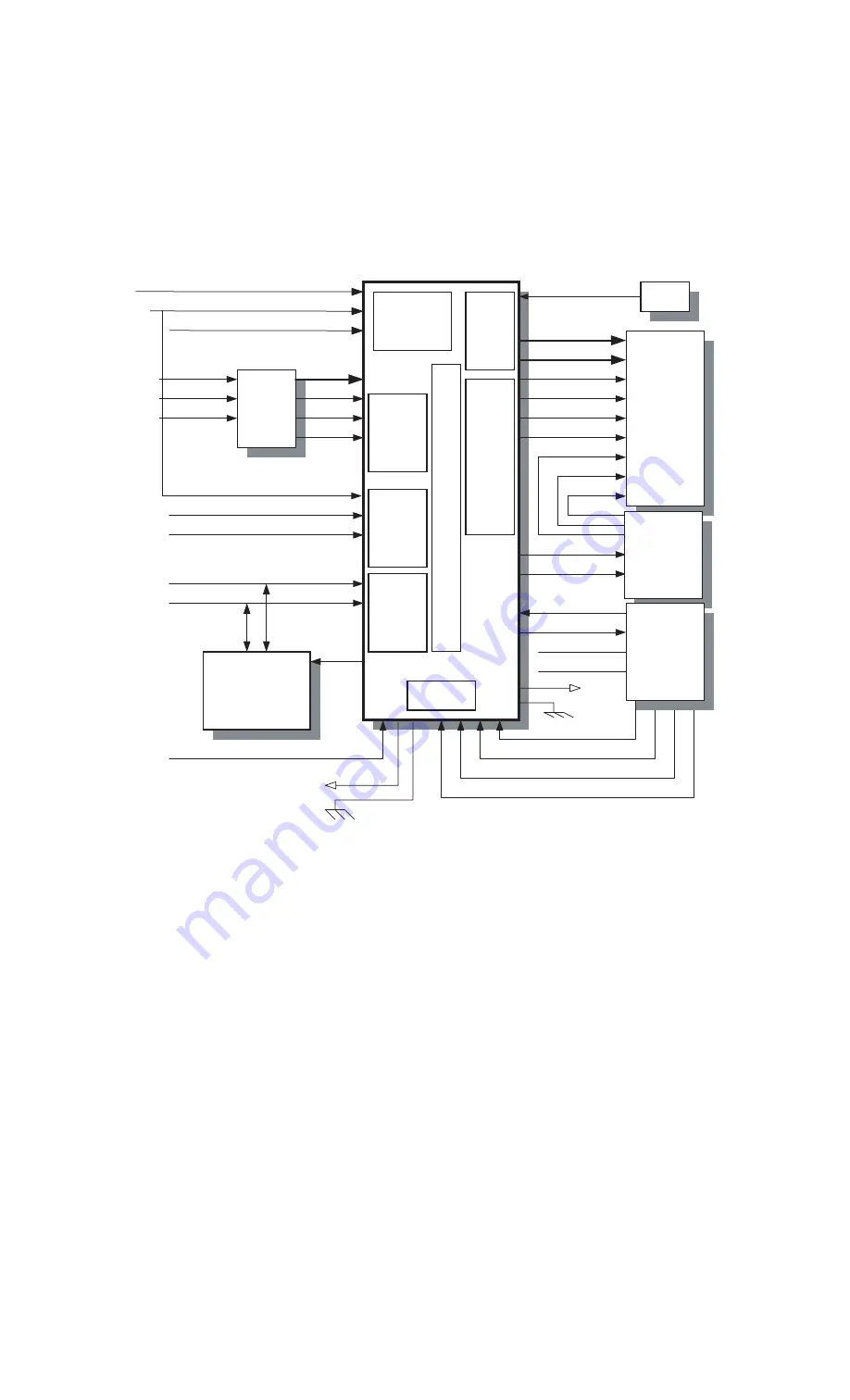

APPENDIX : IC DESCRIPTION

6 – 4

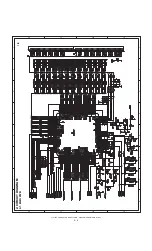

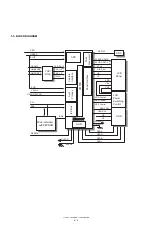

1-3. BLOCK DIAGRAM

CORE

ADC

Sync

Process

I2C Bus

YUV/

RGB

Micro-controller

with EEPROM

OSD

Clock

Generator

Panel Interface

OSC

REFCLK

LCD

Panel

RED

GREEN

BLUE

VSYNC

HSYNC/XSYNC

SCL

SDA

CHROMA

LUMINANCE

COMPOSITE

PA0~PA15

CAP_HS

CAP_VS

TVCLK

IRQ#

RESET#

24 EVEN DATA

24 ODD DATA

PCLK

DISP_EN

HS

VS

VDD

VBL

VEE

VDD Control

VBL Control

VEE Control

OSD-I

OSD-B

OSD-R

OSD-G

OSD-FSW

OSD-CLK

HS

VS

Capture

Interface

LCD

Power-

Switching

Control

OSD

MASCOT

SOG

DCVDD

DCVSS

DOBVDD

DOBVSS