Type Descriptions:

I

Input TTL compatible

IS

Input with Schmitt Trigger

I/O20

Input/Output with 16 mA sink 0.4 V, source 16 mA 2.4 V

I/O24

Input/Output with 24 mA sink 0.4 V, source 12mA 2.4 V

I/O36

Input/Output with 36 mA sink 0.4 V, source 8 mA 2.4 V

ICLK

CLK input at 24 MHz

OCLK

CLK output at 24 MHz

O4

Output with 4 mA 0.4 V, source 4 mA 2.4 V

O16

Output with 16 mA sink 0.4 V, source 8 mA 2.4 V

O20

Output with 16 mA sink 0.4 V, source 16 mA 2.4 V

O24

Output with 24 mA sink 0.4 V, source 12 mA 2.4 V

O36

Output with 36 mA sink 0.4 V, source 8 mA 2.4 V

OD24

Open drain outputs, sinks 24 mA 0.4 V

OD36

Open drain outputs, sinks 36 mA 0.4 V

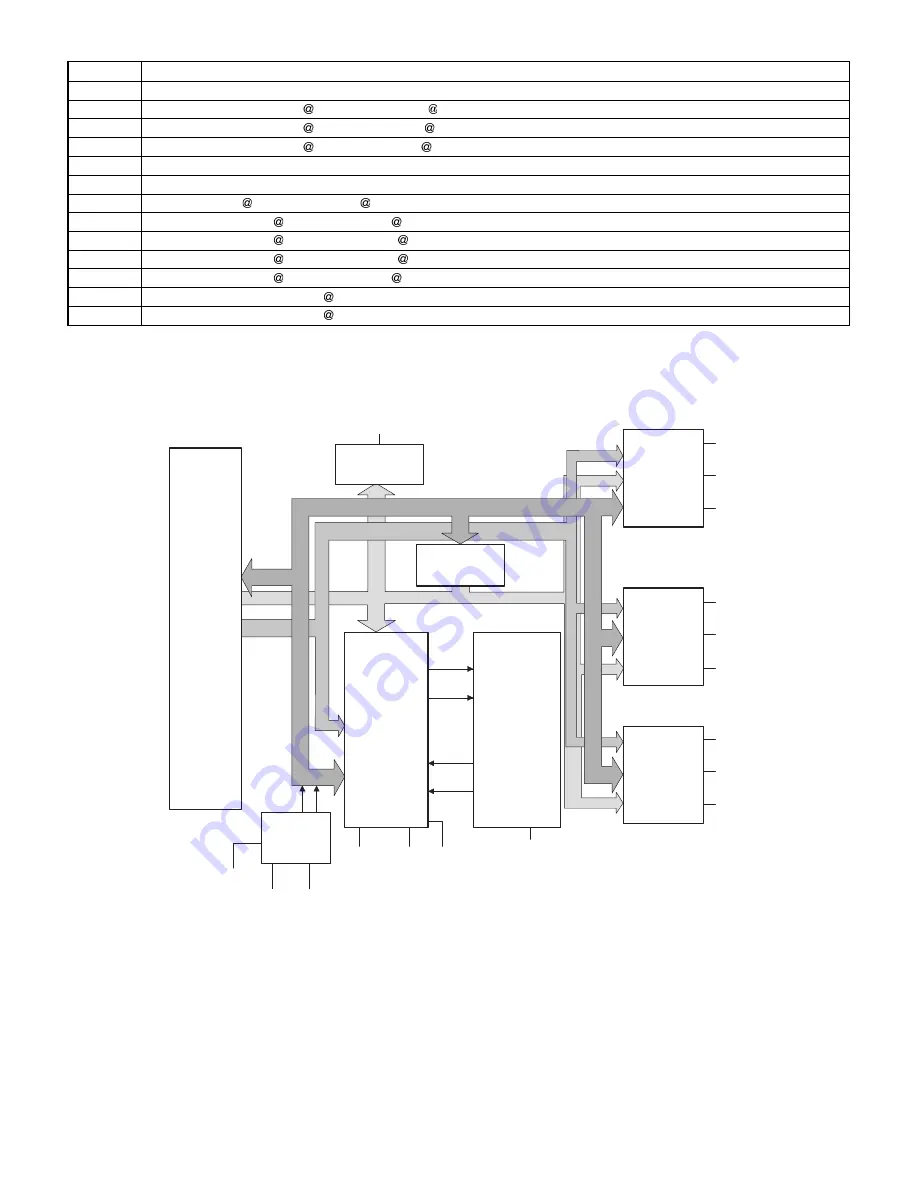

11-4. Functional block diagram

CLK1

CLK2

Clock Gen

SERIAL

CLOCK

Host

CPU

Interface

IORJ

IOWJ

AEN

A0-A9

A0-A7

FDRQ

DACKJ

PINTR3

TC

UR2IRQB

UR2IRQA

UR1IRQB

UR1IRQA

PINTR1

PINTR2

FINTR

RESET

DFRQA

DRQB

DACKA

DACKB

A10

IOCHRDY

PWRGD

Power

Management

DATA BUS

ADDRESS BUS

Configuration

Registers

765A

Compatible

Floppy Disk

Controller

Core

Data

Separator

with Write

Precompensa

tion

WDATA

WCLOCK

RCLOCK

RDATA

WDATAJ,RDATAJ

DS0,1J

MTR0,1J

INDEXJ

TRK0J

DSKCHGJ

WRPRTJ

WGATEJ

DENSEL

DIRJ

STEPJ

DRATE0

DRATE1

HDSELJ

16C550

Compatible

Senal Port 2

with

Infrared

TXD2,CTS2J,

RTS2J,IRTX2

RXD2,IRRX2

DSR2J,DCD2J,

RI2J,DTR2J

16C550

Compatible

Senal Port 1

with

Infrared

TXD1(IRTX),CTS1J,

RTS1J

RXD1(IRRX)

DSR1J,DCD1J,

RI1J,DTR1J

STROBEJ,SLCTINJ,

INITJ,AUTOFDJ

Multi-Mode

Parallel

Port/FDC

MUX

BUSY,SLCT,PE,

ERRORJ,ACKJ

PD0-7

CONTROL BUS

5 – 43

Summary of Contents for UP-5700

Page 139: ...1 UP 5700 Main PWB CHAPTER 10 PWB LAYOUT A side 10 1 ...

Page 140: ...2 UP 5700 CPU PWB A side UP 5700 CPU PWB B side 10 2 ...

Page 141: ...3 UP 5700 KEY I F PWB A side CN2 UP 5700 KEY I F PWB B side 10 3 ...

Page 144: ...For components produced in January 1998 and onward Parts side Solder side 10 6 ...

Page 145: ...7 2 Sub PWB Side A Side B 10 7 ...