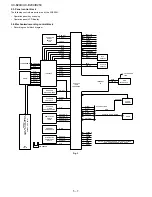

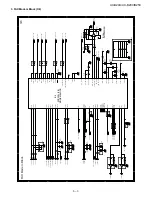

UX-B20U/UX-B20C/B25C

5 – 11

µ

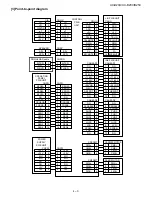

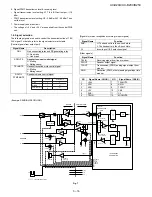

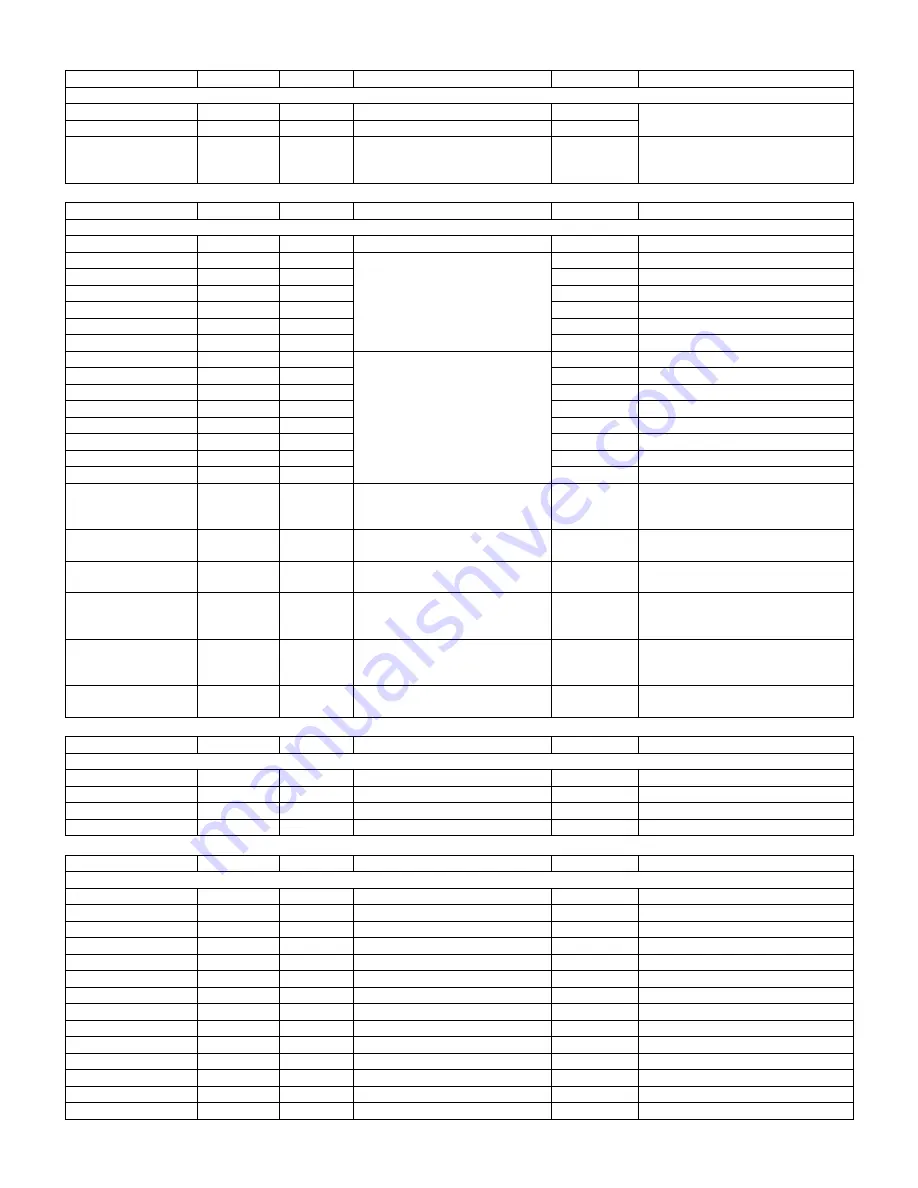

PD65945 (IC4) Pin descriptions

SYMBOL

PIN NO.

I/O

DESCRIPTION

PAD CELL.

NOTE

System Operation Signals (3 pin)

XIN

75

I

X’tal in

OSI1

32.256 MHz

XOUT

74

O

X’tal out

OSO1

ASICRES

70

I

Reset

L: Operate

H: Reset

FIS1

Schmitt

SYMBOL

PIN NO.

I/O

DESCRIPTION

PAD CELL.

NOTE

Fax Engine Bus Interface (21 pin)

SYSCLK

83

O

System clock for Fax Engine

FE04

32.256 MHz Output

A0

104

I

Address bus

L: Logic 0

H: Logic 1

FI01

A1

103

I

FI01

A2

102

I

FI01

A3

101

I

FI01

A4

100

I

FI01

A5

99

I

FI01

D0

95

I/O

Data bus

L: Logic 0

H: Logic 1

B00C

D1

94

I/O

B00C

D2

93

I/O

B00C

D3

92

I/O

B00C

D4

91

I/O

B00C

D5

90

I/O

B00C

D6

89

I/O

B00C

D7

88

I/O

B00C

CS_N

68

I

Chip select

L: Select

H: Deselect

FI01

Schmitt

RD_N

106

I

Read strobe

L: Read

FI01

Schmitt

WR_N

107

I

Write strobe

L: Write

FI01

Schmitt

INT_N

67

O

Interrupt

L: Interrupt

Hi-Z: No Interrupt

EXTH

Open Drain

RDY

61

O

External Wait

L: Wait

Hi-Z: Ready

EXTH

Open Drain

SCANSYNC

60

I

Scanner Motor Sync. Signal

Rise: Sync.

FISI

Schmitt

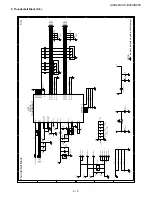

SYMBOL

PIN NO.

I/O

DESCRIPTION

PAD CELL.

NOTE

Thunderbolt Control Interfaces (4 pin)

SCS_N

141

O

Chip Select

FO09

SCLK

142

O

Clock

FO09

SDAT

140

O

Data

FO09

SRST_N

133

I

Reset

FISI

Schmitt

SYMBOL

PIN NO.

I/O

DESCRIPTION

PAD CELL.

NOTE

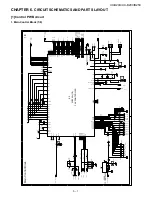

Spitfire Control Signals (14 pin)

SFRES_N

127

O

Reset

FE04

ACLK

130

O

A-Line Counter Clock

FE04

AGATE

129

O

Reset A-Line to Low

FE04

PLCLK

128

O

Shift Clock for P-Line Data

FE04

PDATA0

120

O

Serial Data Output#0

FE04

PDATA1

119

O

Serial Data Output#1

FE04

PDATA2

118

O

Serial Data Output#2

FE04

PDATA3

117

O

Serial Data Output#3

FE04

PLOAD

113

O

Latches into Holding Reg.

FE04

PENABLE

114

O

Enables P-Line Output Drive

FE04

LCN

111

O

Latch Control Register

FE04

LHCS

112

O

Latch Heater States

FE04

OK2PRT

125

I

P-Line Driver Status

FISI

Schmitt

PHID

126

I

Print Head ID Compare Status

FISI

Schmitt

Summary of Contents for UX-B20

Page 2: ... i UX B20U UX B20C B25C ...