Summary of Contents for SA 400 minifloppy

Page 1: ...SA400 CQ m minifloppyTM DisketteStorageDrive 2 C J ...

Page 2: ...SA400 CQ m minifloppyTM DisketteStorageDrive 2 C J Copyright 1977 Shugart Associates ...

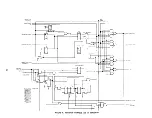

Page 7: ...FIGURE 1 SA400 MINIFLOPPY DRIVE ...

Page 17: ...THIS PAGE INTENTIONALLY LEFT BLANK 10 ...

Page 23: ...THIS PAGE INTENTIONALLY LEFT BLANK 16 ...