CPU Functions

C500 Family

Semiconductor Group

2-11

1998-04-01

Any of these three conditions will block the generation of the LCALL to the interrupt service routine.

Condition 2 ensures that the instruction in progress is completed before vectoring to any service

routine. Condition 3 ensures that if the instruction in progress is RETI or any write access to interrupt

enable or interrupt priority registers, then at least one more instruction will be executed before any

interrupt is vectored too; this delay guarantees that changes of the interrupt status can be observed

by the interrupt controller.

The polling cycle is repeated with each machine cycle, and the values polled are the values that

were present at the previous machine cycle. Note that if any interrupt flag is active but not being

responded to for one of the conditions already mentioned, or if the flag is no longer active when the

blocking condition is removed, the denied interrupt will not be serviced. In other words, the fact that

the interrupt flag was once active but not serviced is not remembered. Every polling cycle

interrogates only the pending interrupt requests.

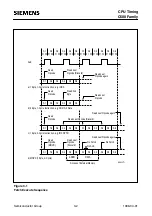

The polling cycle/LCALL sequence is illustrated in

.

Figure 2-5

Interrupt Detection/Entry Diagram

Note that if an interrupt of a higher priority level goes active prior to S5P2 in the machine cycle

labeled C3 in

then, in accordance with the above rules, it will be vectored to during C5

and C6 without any instruction for the lower priority routine to be executed.

Thus, the processor acknowledges an interrupt request by executing a hardware-generated LCALL

to the appropriate servicing routine. In some cases it also clears the flag that generated the

interrupt, while in other cases it does not; then this has to be done by the user's software.

The program execution proceeds from that location until the RETI instruction is encountered. The

RETI instruction informs the processor that the interrupt routine is no longer in progress, then pops

the two top bytes from the stack and reloads the program counter. Execution of the interrupted

program continues from the point where it was stopped. Note that the RETI instruction is very

important because it informs the processor that the program left the current interrupt priority level.

A simple RET instruction would also have returned execution to the interrupted program, but it

would have left the interrupt control system thinking an interrupt was still in progress. In this case no

interrupt of the same or lower priority level would be acknowledged.

MCT01859

S5P2

Interrupt

is latched

Interrupts

are polled

Vector Address

Long Call to Interrupt

Routine

Interrupt

C2

C1

C3

C4

C5