Semiconductor Group

2-12

1998-04-01

CPU Functions

C500 Family

2.8

Interrupt Response Time

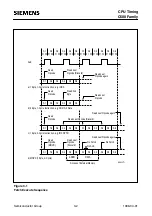

If an external interrupt is recognized, its corresponding request flag is set at S5P2 in every machine

cycle. The value is not polled by the circuitry until the next machine cycle. If the request is active and

conditions are right for it to be acknowledged, a hardware subroutine call to the requested service

routine will be next instruction to be executed. The call itself takes two cycles. Thus a minimum of

three complete machine cycles will elapse between activation and external interrupt request and the

beginning of execution of the first instruction of the service routine.

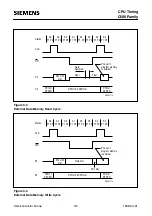

A longer response time would be obtained if the request was blocked by one of the three previously

listed conditions. If an interrupt of equal or higher priority is already in progress, the additional wait

time obviously depends on the nature of the other interrupt's service routine. If the instruction in

progress is not in its final cycle, the additional wait time cannot be more than 3 cycles since the

longest instructions (MUL and DIV) are only 4 cycles long; and, if the instruction in progress is RETI

or a write access to interrupt enable or interrupt priority registers the additional wait time cannot be

more than 5 cycles (a maximum of one more cycle to complete the instruction in progress, plus 4

cycles to complete the next instruction, if the instruction is MUL or DIV).

Thus a single interrupt system, the response time is always more than 3 cycles and less than

9 cycles.