CPU Timing

C500 Family

Semiconductor Group

3-1

1998-04-01

3

CPU Timing

3.1

Basic Timing

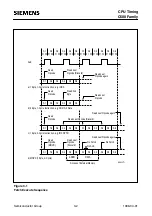

A machine cycle consists of 6 states. Each state is divided into a phase 1 half, during which the

phase 1 clock is active, and a phase 2 half, during which the phase 2 clock is active. Thus, a

machine cycle consists of the states S1P1 (state 1, phase 1) through S6P2 (state 6, phase 2).

Depending on the C500 type of microcontroller, each state lasts either one or two periods of the

oscillator clock. Typically, arithmetic and logical operations take place during phase 1 and internal

register-to-register transfers take place during phase 2.

The diagrams in

show the fetch/execute timing related to the internal states and phases.

Since these internal clock signals are not user-accessible, the ALE (address latch enable) signal is

shown for external reference. ALE is normally activated twice during each machine cycle: once

during S1P2 and S2P1, and again during S4P2 and S5P1.

The execution of a one-cycle instruction begins at S1P2, when the opcode is latched into the

instruction register. If it is a two-byte instruction, the second reading takes place during S4 of the

same machine cycle. If it is a one-byte instruction, there is still a fetch at S4, but the byte read (which

would be the next op-code) is ignored (discarded fetch), and the program counter is not

incremented. In any case, execution is completed at the end of S6P2.

and

(b)

show the timing of a 1-byte, 1-cycle instruction and for a 2-byte, 1-cycle

instruction.

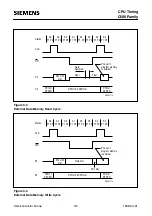

Most C500 instructions are executed in one cycle. MUL (multiply) and DIV (divide) are the only

instructions that take more than two cycles to complete; they take four cycles. Normally two code

bytes are fetched from the program memory during every machine cycle. The only exception to this

is when a MOVX instruction is executed. MOVX is a one-byte, 2-cycle instruction that accesses

external data memory. During a MOVX, the two fetches in the second cycle are skipped while the

external data memory is being addressed and strobed.

and

(d)

show the timing for

a normal 1-byte, 2-cycle instruction and for a MOVX instruction.