Semiconductor Group

6-62

1999-04-01

On-Chip Peripheral Components

C541U

The device interrupt enable register DIER contains the enable bits for the different types of device

interrupts. With these bits, the device interrupts can be individually enabled or disabled. The general

device interrupt enable bit EUDI is located in SFR IEN1. A device interrupt can be only generated

if EUDI and EA (global interrupt enable bit in IEN0) are set too.

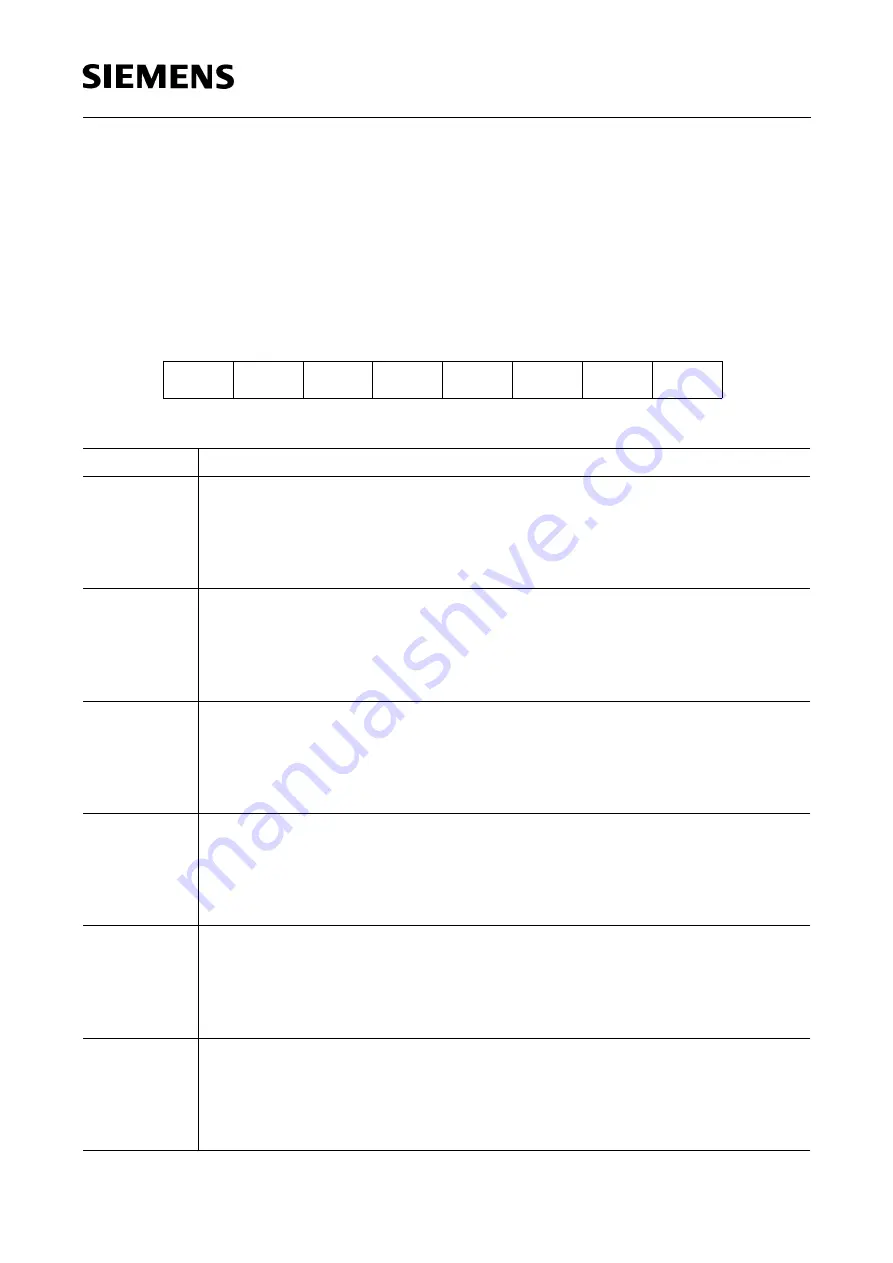

USB Device Interrupt Enable Register DIER (Address C3H) Reset Value : 00H

Bit

Function

SE0IE

Single ended zero Interrupt Enable

Setting bit SE0IE enables the generation of a device interrupt each time a single

ended zero is detected for more than 2.5µs (reset by host, not EOP).

If SE0IE=0, the single ended zero interrupt is disabled.

If SE0IE=1, the single ended zero interrupt is enabled.

DAIE

Device attached interrupt enable

Setting bit DAIE enables the generation of a device interrupt when it is attached

to the USB bus.

If DAIE=0, the device attached interrupt is disabled.

If DAIE=1, the device attached interrupt is enabled.

DDIE

Device detached interrupt enable

Setting bit DDIE enables the generation of a device interrupt when it is detached

from the USB bus.

If DDIE=0, the device detached interrupt is disabled.

If DDIE=1, the device detached interrupt is enabled.

SBIE

Suspend begin interrupt enable

Setting bit SBIE enables the generation of a device interrupt if bit SBI is set, this

means the suspend mode is entered.

If SBIE=0, the suspend begin interrupt is disabled.

If SBIE=1, the suspend begin interrupt is enabled.

SEIE

Suspend change interrupt enable

Setting bit SEIE enables the generation of a device interrupt if bit SEI is set, this

means the suspend mode is left.

If SEIE=0, the suspend change interrupt is disabled.

If SEIE=1, the suspend change interrupt is enabled.

STIE

Status interrupt enable

Bit STIE enables the generation of a device interrupt at the end of the status phase

of a control transfer.

If STIE=0, the status interrupt is disabled.

If STIE=1, the status interrupt is enabled.

MSB

LSB

DIER

SE0IE

DAIE

DDIE

SBIE

SEIE

STIE

SUIE

SOFIE

7

6

5

4

3

2

1

0

Bit No.

rw

rw

rw

rw

rw

rw

rw

rw

C3H

Summary of Contents for C541U

Page 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Page 7: ......

Page 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Page 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

Page 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Page 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Page 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...