Sequence

The location used is the low byte of the word addressed by the BR

register plus the constant. If the content of the low byte is ’0’, the TSG

operation enters the slot ID in the location.

Testing (reading) and possible occupation of the location (writing)

form a program unit that cannot be interrupted.

Result

You can evaluate the result of the test using condition codes CC 0 and

CC 1:

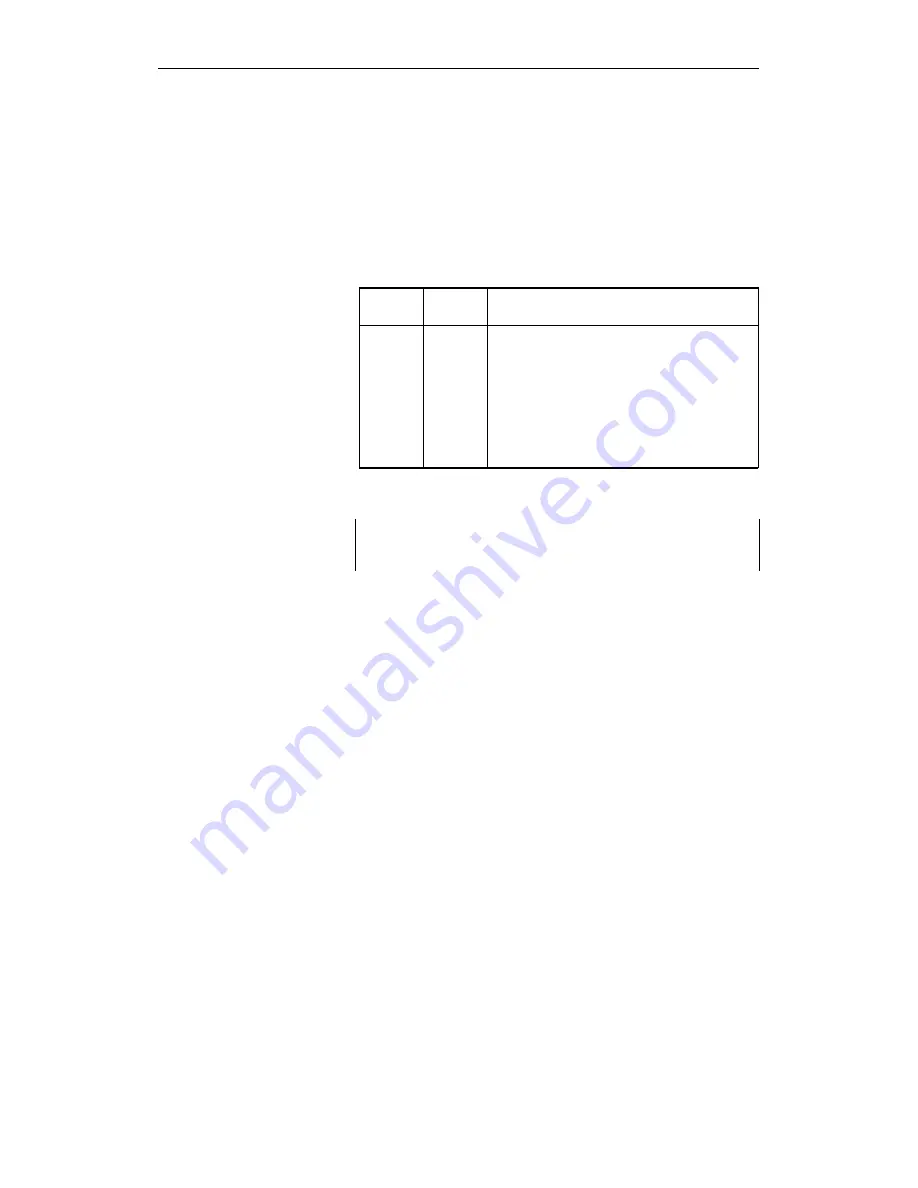

CC 1

CC 0

Description

0

1

0

0

0

1

The "occupied" register contains ’0’. The CPU

enters its own slot ID.

The slot ID of the CPU is already entered

in the "occupied" register.

The "occupied" register contains a

different slot ID.

Note

All CPUs that require synchronized access to a common global

memory area must use the TSG operation.

Error reaction

The absolute address must be between F 0000H and F FFFFH. If the

absolute addresses are not in the range shown, the CPU detects a

transfer error (TRAF) and calls OB 32. If OB 32 is not loaded, the

CPU changes to the STOP mode with the error code TRAF (ISTACK).

Operations with the Base Address Register (BR Register)

CPU 948 Programming Guide

9 - 26

C79000-G8576-C848-04

Summary of Contents for CPU 948

Page 10: ...Contents CPU 948 Programming Guide 1 2 C79000 G8576 C848 04 ...

Page 32: ...Contents CPU 948 Programming Guide 2 2 C79000 G8576 C848 04 ...

Page 72: ...Data Blocks CPU 948 Programming Guide 2 42 C79000 G8576 C848 04 ...

Page 74: ...Contents CPU 948 Programming Guide 3 2 C79000 G8576 C848 04 ...

Page 154: ...Contents CPU 948 Programming Guide 4 2 C79000 G8576 C848 04 ...

Page 200: ...Contents CPU 948 Programming Guide 5 2 C79000 G8576 C848 04 ...

Page 308: ...Contents CPU 948 Programming Guide 7 2 C79000 G8576 C848 04 ...

Page 324: ...Examples of Parameter Assignment CPU 948 Programming Guide 7 18 C79000 G8576 C848 04 ...

Page 326: ...Contents CPU 948 Programming Guide 8 2 C79000 G8576 C848 04 ...

Page 370: ...Addressable System Data Area CPU 948 Programming Guide 8 46 C79000 G8576 C848 04 ...

Page 372: ...Contents CPU 948 Programming Guide 9 2 C79000 G8576 C848 04 ...

Page 486: ...Contents CPU 948 Programming Guide 11 2 C79000 G8576 C848 04 ...

Page 522: ...PG Functions via the S5 Bus CPU 948 Programming Guide 11 38 C79000 G8576 C848 04 ...

Page 524: ...Contents CPU 948 Programming Guide 12 2 C79000 G8576 C848 04 ...

Page 538: ...Contents CPU 948 Programming Guide 13 2 C79000 G8576 C848 04 ...

Page 546: ...List of Key Words CPU 948 Programming Guide Index 6 C79000 G8576 C848 04 ...