Systemsoftware

System- and communication configuring D7-SYS - SIMADYN D

2-33

Edition 03.2001

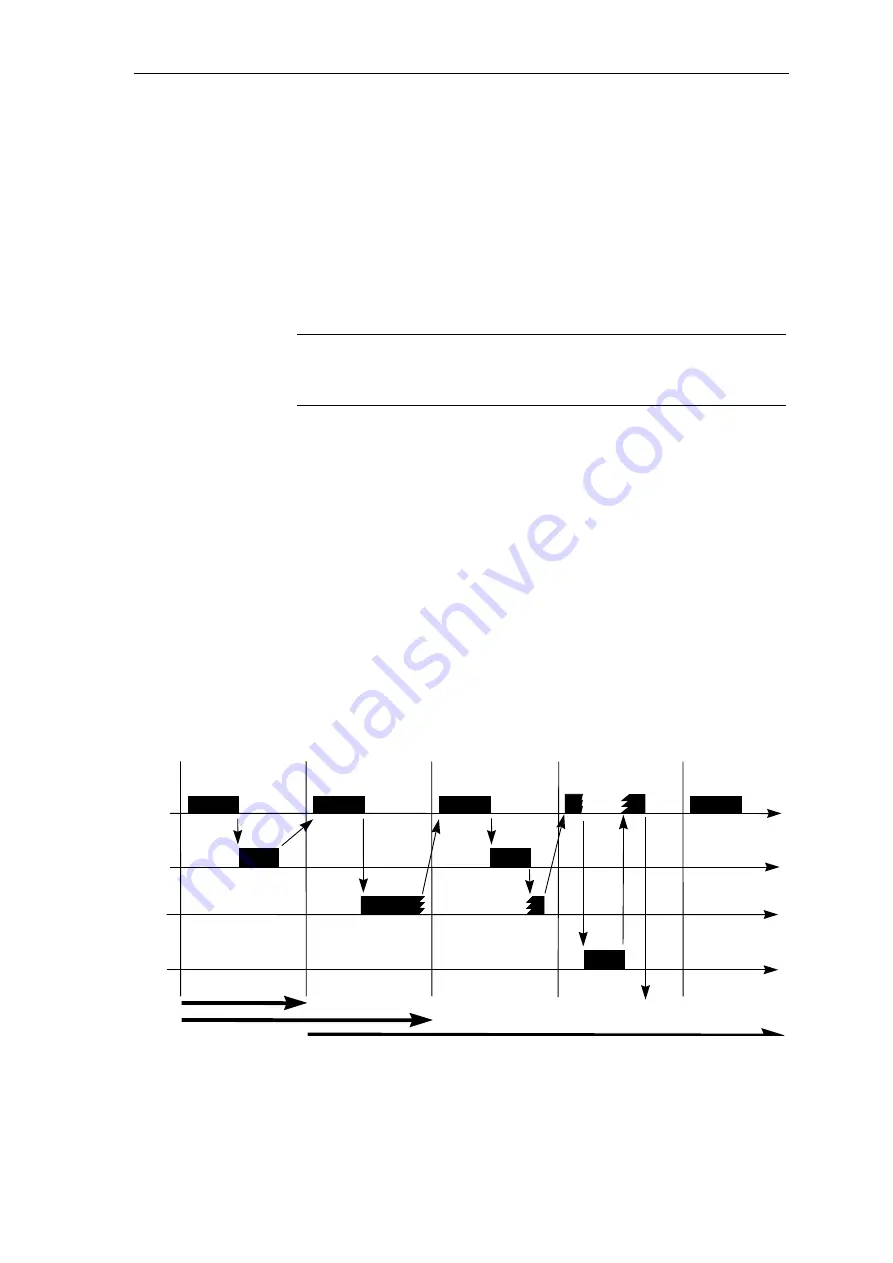

If a task can no longer be completed within a basic sampling time due to

a higher computation time, then it is completed in the following basic

cycles. The tasks with short sampling times are completed before tasks

with long sampling times, i. e. T1 before T2, before T3 before T4 before

.... This distribution is permissible, i. e. without cycle error, as long as the

required sampling times are maintained (refer to the 2nd and 3rd cycle).

If the computation time loading becomes higher, for the task with the

longest sampling time, at same stage a cycle error will occur. This means

that the sum of the function blocks cannot be computed completely within

the configured sampling time.

NOTE

If a specific number of cycle errors is exceeded, an "E" error ID is set,

and is displayed in the 7-segment display on the front panel of the CPU,

if this is the highest priority error status of the CPU at this time.

In addition to the configurable interrupt tasks, the cyclic tasks are

interrupted, especially by communication interrupts. These interrupts

ensure that, for example, the data to be transmitted and received via the

serial interfaces is processed before new data is received. Transmit- and

receive interrupts such as these can occur independently of the

configured cycle time of the appropriate communication blocks at almost

any instant in time. As result of this, and the unpredictable occurrence of

interrupt tasks, if the process utilization is extremely high, each cyclic task

can generate one or several cycle errors due to task back-up.

This can be especially noticed, if

•

the utilization by the task with the lowest sampling time is extremely

high, and

•

the functions computed in this task are extremely sensitive to sporadic

sampling cycle failures, (e. g. closed-loop position controls).

T1

T2

T1+T2

T1+T2

T1+T3

T1+interrupt task+T4

T1

T3

T4

In this

T2 = 2 * T1

T3 = 4 * T1

T1

T2

T3

Interrupt

task

Fig. 2-12

Sequence of a configured task

Cycle errors