Copyright © Siemens AG 2016. All rights reserved

173

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

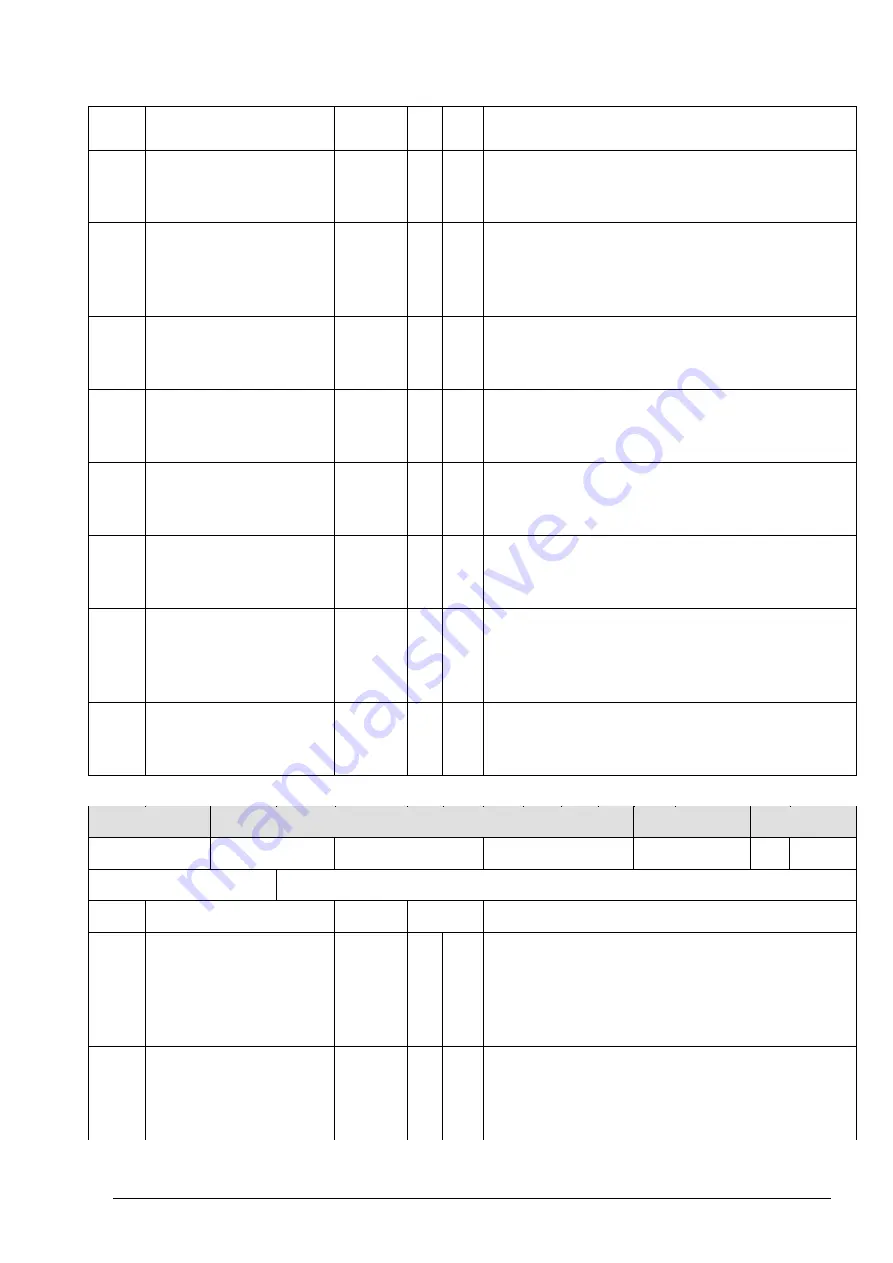

10 = reserved

11 = Burstflash ROM

6dt4 R_HOLD

7h

r w

Read Hold Cycles

Hold Phase of read access lasts (

1) clocks.

12dt7 R_STROBE

3Fh

r w

Read Strobe Duration Cycles

Strobe Phase of read access (Read Enable =

0) lasts (R_ 1) clocks.

Value 0 is not supported.

16dt13 R_SU

Fh

r w

Read Setup Cycles

Setup Phase of read access lasts R_SU

clocks.

19dt17 W_HOLD

7h

r w

Write Hold Cycles

Hold Phase of write access lasts (

1) clocks.

25dt20 W_STROBE

3Fh

r w

Write Strobe Duration Cycles

Strobe Phase of write access (Write Enable =

0) lasts (W_ 1) clocks.

29dt26 W_SU

Fh

r w

Write Setup Cycles

Setup Phase of write access lasts W_SU

clocks.

30

EW

0h

r w

Extend Wait mode

0 = WAIT input = don't care

1 = Wait input extends access (valid in SRAM

mode only)

31

WSM

0h

r w

Wait input synchronisation mode

0 = 2 Flipflops

1 = 1 Flipflop

Register:

ASYNC_BANK1

Address:

14h

Bits:

31dt0

Reset value:

3FFFFFF2h

Attributes: r w

Description:

Async. Bank 1 Configuration register

Bit

Identifier

Reset Attr.

Function / Description

1dt0 SIZE

2h

r w

Bank Size

00 = 8 bit device

01 = 16 bit device

10 = 32 bit device

11 = reserved

3dt2 MODE

0h

r w

Mode

00 = SRAM

01 = Pagemode ROM

10 = reserved