Copyright © Siemens AG 2016. All rights reserved

303

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

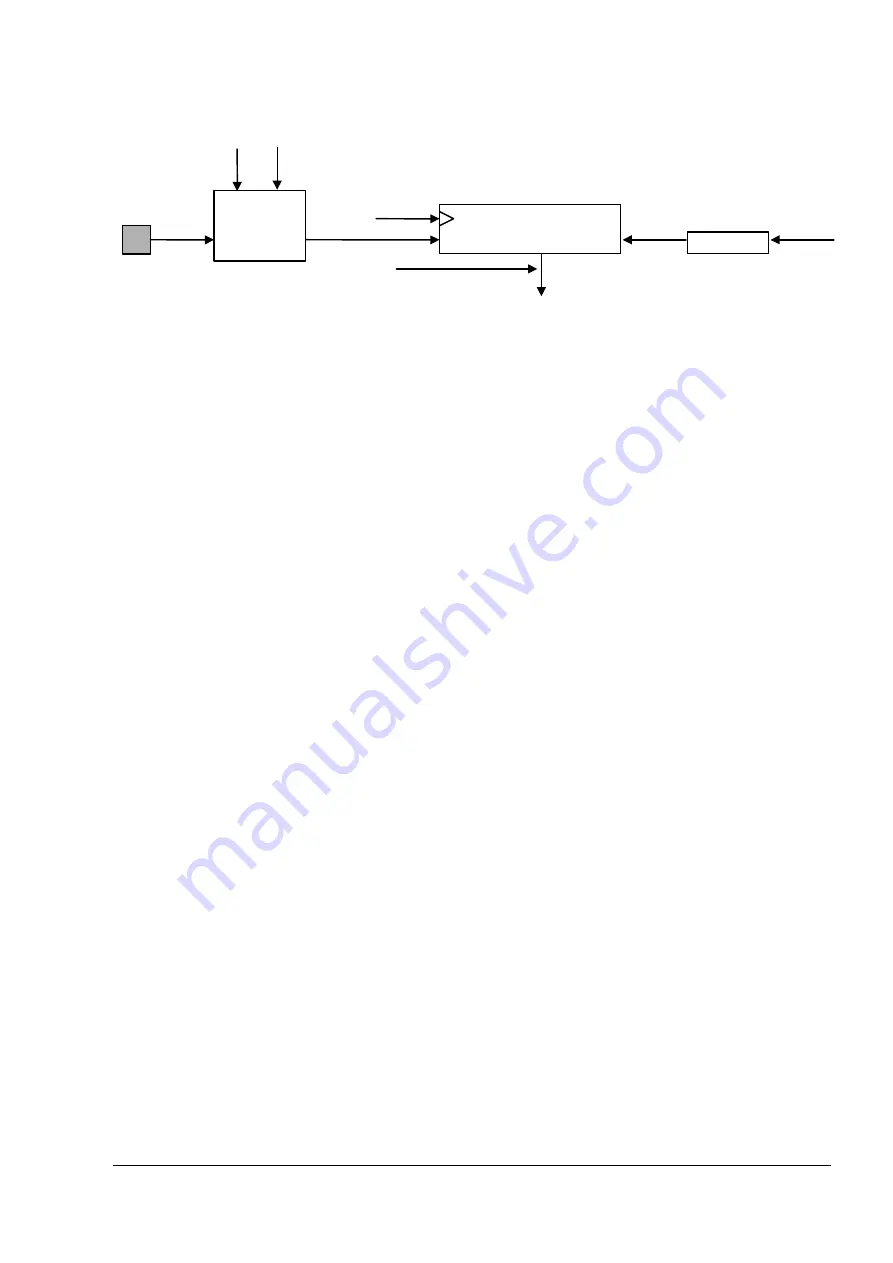

The F-counter is triggered with a separate BYP_CLK input. The F-counter cannot be

triggered in clock bypass mode (CONFIG(2)='1') (see 2.3.10.9.3

X

).

32-Bit Down-Counter

F-Counter-Val(31:0)

F-COUNTER-EN

BYP_CLK

Sync Stage:

3

edge

enable

DIRECT_IN

Read: F-Counter-Val

FCOUNT_RES

Reset

Write: F-Counter-Res

Data = 0xXXXX 55AAh

CLK_APB

CLK_APB

EN

APB-Bus

F_CLK

CONFIG(2)

Figure 38: F-timer block diagram

2.3.10.4.1

Function Description

The asynchronous input signal F_CLK of the external independent time base is connect-

ed to a synchronization stage with the input pin BYP_CLK. The SYNC stage is imple-

mented with 3 FF stages to prevent metastable states arising at the counter input.

In a downstream stage for edge detection, the count pulses (F-Counter-EN) are generat-

ed and connected to the 32-bit down counter. All flip-flops in the circuit operate with the

APB clock (125 MHz).

The 32-bit counter is reset to 0x0000 0000h with an asynchronous block reset (XRESET,

XSRST not shown in

Figure 38: F-timer block diagramFigure 38). The next counter pulse

sets the counter to 0xFFFF FFFFh. Each subsequent pulse decrements the counter val-

ue. When the counter reaches 0x0000 0000h, the next counter pulse triggers a wrapa-

round to 0xFFFF FFFFh. Writing a value of 0xXXXX 55AAh (X:= don’t care) to the ad-

dress of the F-counter reset register (word or halfword) sets the FCOUNTER_RES regis-

ter (see 2.3.10.4.3), which resets the 32-bit counter to 0x0000 0000h. The

FCOUNTER_RES register is automatically reset to 0 one clock cycle later.

With read access (word) to the F-Counter, the complete 32-bit counter is switched to the

APB bus. Word access is required to ensure that the counter value is read consistently.

Halfword and byte access is technically possible, but will return an inconsistent counter

value.

2.3.10.4.2 Application Information

The maximum input frequency permitted for F_CLK is ¼ of the APB clock upon quartz

failure with a 50% duty cycle.

In standard operation, the PLL outputs 500 MHz with a quartz supply of 25 MHz.

A minimum output frequency is established at the PLL following quartz failure at the

ERTEC 200P. This free-running PLL frequency is 100 - 300 MHz. The min. APB_CLK

frequency following quartz failure is therefore PLLOUT

min

/4 (~ 25 MHz).

For safety reasons, the external independent F-CLK should be a maximum of ¼ of the

minimum possible APB clock (following quartz failure) in order to prevent any errors in

edge detection.

The current setting is for an independent F-CLK of 32768 Hz. This ensures a safe differ-

ence from the internal system clock.

2.3.10.4.3

Address Mapping