Copyright © Siemens AG 2016. All rights reserved

317

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

9

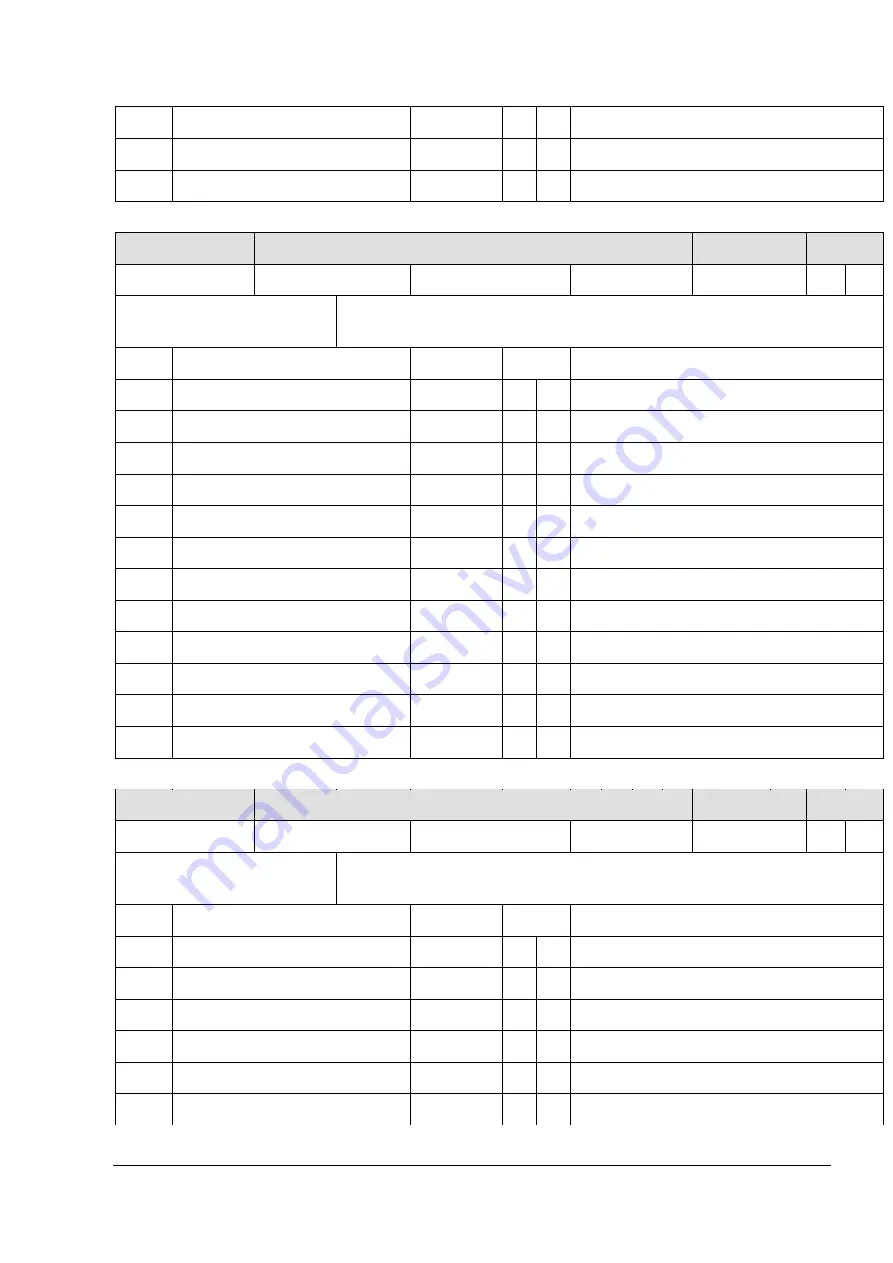

Break_Error_Mask

0h

r w

10

Overrun_Error_Mask

0h

r w

31dt11 <unused>

000000h r

Reserved, do not modify, read as zero.

Register:

UARTRIS

Address:

3Ch

Bits:

31dt0

Reset value:

0h

Attributes:

r(h)

Description:

Raw Interrupt Status Register

Gives the raw interrupt state (prior to masking) of the interrupt

Bit

Identifier

Reset

Attr.

Function / Description

0

RI_Modem_Int_Status

0h

rh

1

CTS_Modem_Int_Status

0h

rh

2

DCD_Modem_Int_Status

0h

rh

3

DSR_Modem_Int_Status

0h

rh

4

Rx_Int_Status

0h

rh

5

Tx_Int_Status

0h

rh

6

Rx_Timout_Int_Status

0h

rh

7

Framing_Error_Int_Status 0h

rh

8

Parity_Error_Int_Status

0h

rh

9

Break_Err_Int_Status

0h

rh

10

Overrun_Err_Int_Status

0h

rh

31dt11 <unused>

000000h r

Reserved, do not modify, read as zero.

Register:

UARTMIS

Address:

40h

Bits:

31dt0

Reset value:

0h

Attributes:

r(h)

Description:

Mask Interrupt Status Register

Gives the masked interrupt state (after masking) of the interrupt

Bit

Identifier

Reset

Attr.

Function / Description

0

RIMMIS

0h

rh ...RI Intr.

1

CTSMMIS

0h

rh ...CTS Intr.

2

DCDMMIS

0h

rh ...DCD Intr.

3

DSRMMIS

0h

rh ...DSR Intr.

4

RXMIS

0h

rh ...Receive Interrupt

5

TXMIS

0h

rh ...Transmit Interrupt