Copyright © Siemens AG 2016. All rights reserved

383

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

1: Lock enabled

2 reserved

0h

r w

5dt3 reserved

6 ARB

0h

r w

Select arbitration algorithm for AHB

arbiter (ARB_MODE):

0: Round-robin

1: Fixed priority assignment

This bit should not be changed (de-

fault: round robin)! (see 5.3.1.1)

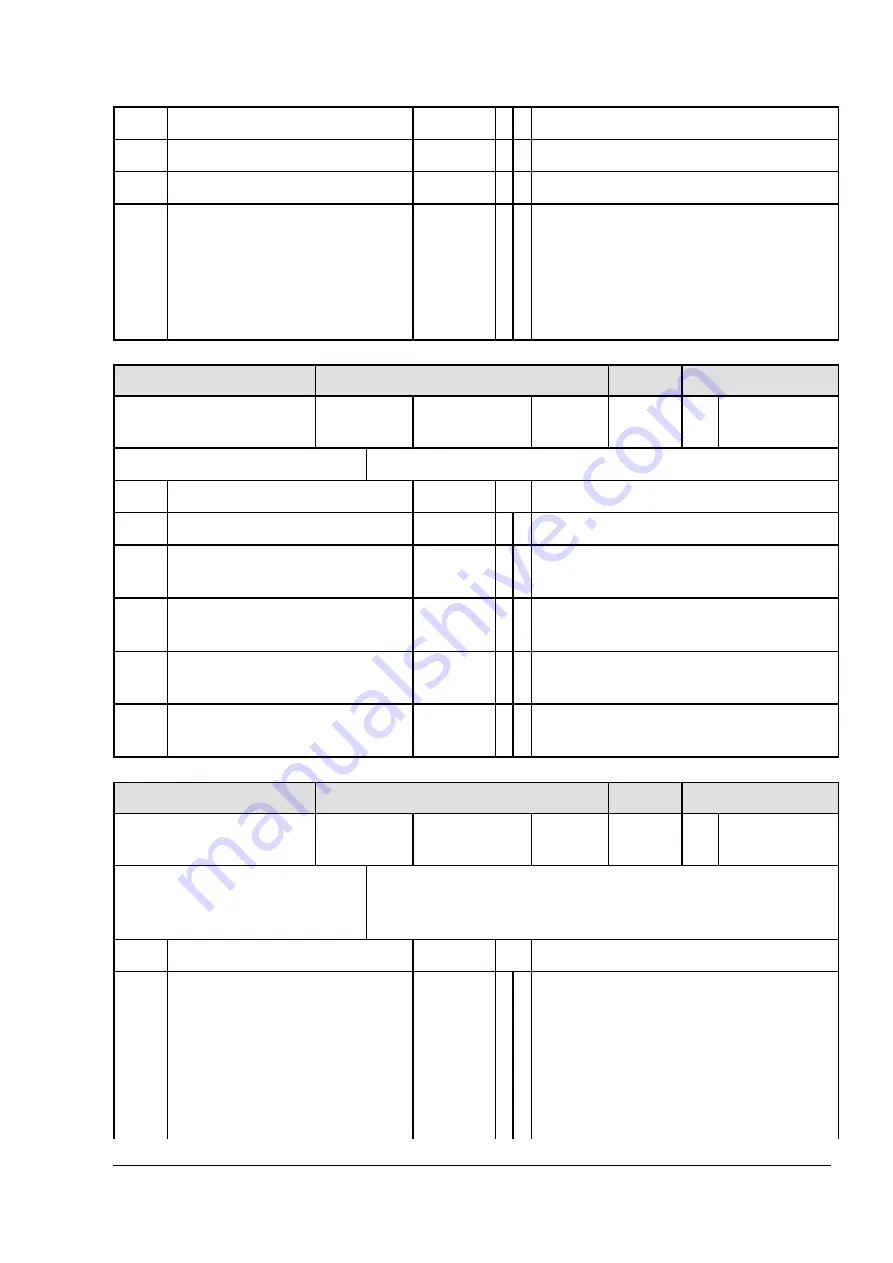

Register:

ERTEC 200PLUS_TAG

Address: 38h

Bits:

31dt0

Reset value:

0000101

3h

Attribu-

tes:

r

Description:

Tag number of current revision

Bit Identifier

Reset Attr. Function / Description

10dt0 R_LABEL

13h

r R-Label

15dt1

1

INKREMENT_NR

2h

r

Increment no. (see ID_REG slice

HW_R)

18dt1

6

PATCH_NR

0h

r

Patch no. (see ID_REG slice

MET_FIX)

20dt1

9

PLATFORM

0h

r

Platform:00 = ASIC, 01 = FPGA, 10 =

reserved, 11 = user-defined

31dt2

1

IDENTIFICATION

0h

r Identification (not used)

Register:

PHY_CONFIG

Address: 3Ch

Bits:

31dt0

Reset value: 0h

Attribu-

tes:

(r)(h

)

(w)

Description:

Configuration of PHY1 and PHY2

Important: PHY_CONFIG register is only reset with an

asynchronous PN-IP reset.

Bit Identifier

Reset Attr. Function / Description

0 P1_PHY_ENB

xh

r

h

w

0: PHY1 disabled (power down mode)

-

Comment: If the PHY is 'Disabled'

and then 'Enabled' again, the SW

must comply with a disable time of -

100?s (see Figure 37 - FSpec ERTEC

200P).

1: PHY1 enabled -