Copyright © Siemens AG 2016. All rights reserved

490

ERTEC 200P-2 Manual

Technical data subject to change

Version

1.0

4.8.5 Readiness of internal resources once a reset is cleared

Please note that access, for example over the XHIF interface, to internal ERTEC 200P

resources immediately after a reset is cleared is only permitted once all internal initializa-

tion actions are complete (see also boot mode startup times in 2.3.1.5.1.4).

Duration of initialization actions after XRESET deactivation:

PLL standby duration: 2.5 µs (see 0)

PLL lockup duration: 1000.0 µs (see 2.3.9.2)

EMC Init_Done

1)

: 233.0 s

Total duration:

1235.5 s

1)

Alongside EMC Init_Done (see also SDRAM_Refresh register in 2.3.5.8), a number of internal SRAMs are also initial-

ized during this time (see also EDC_INIT_DONE register in 2.3.10.9.22). EMC INIT_Done is detailed here as it takes the

longest.

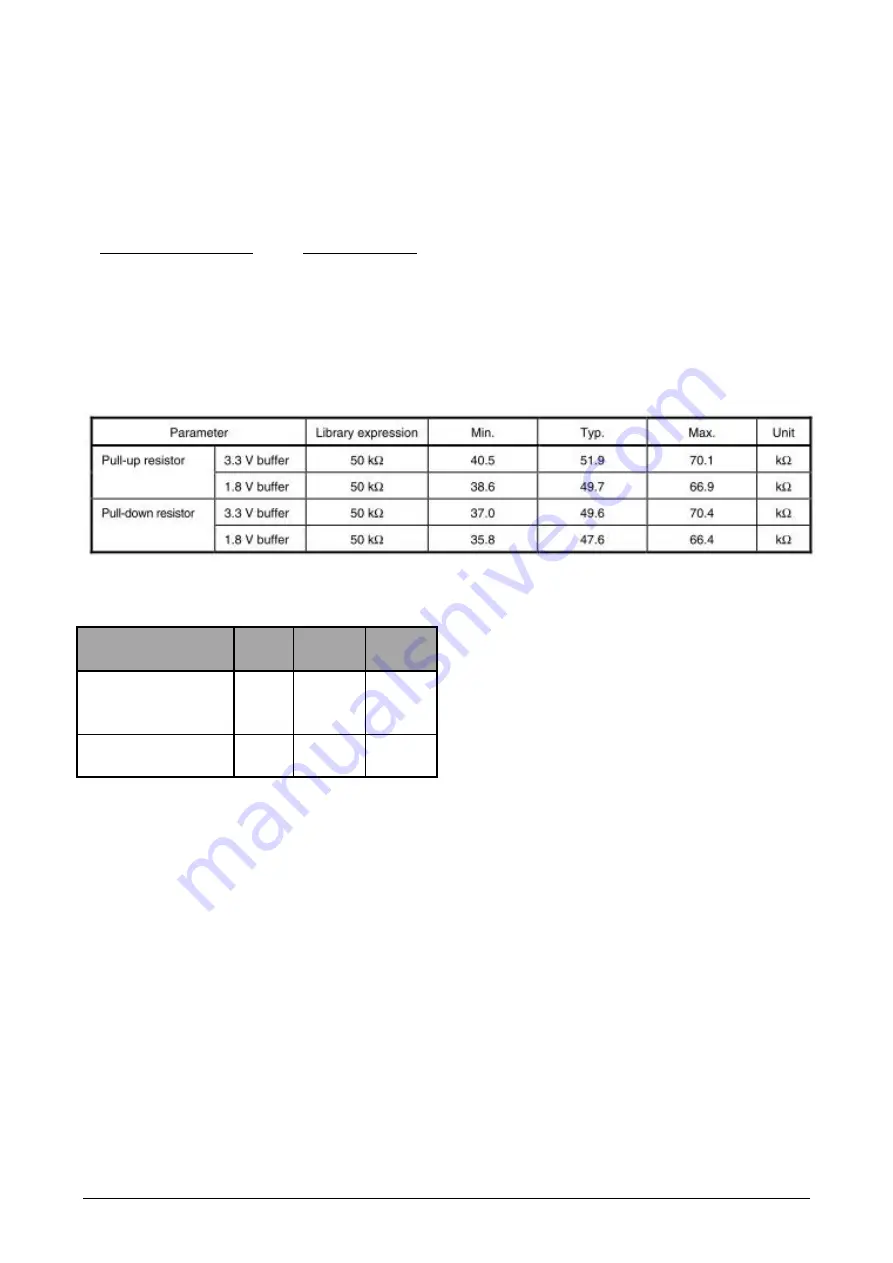

4.9 Pull-up/Pull-down Resistor Values

(V

DD

= 3.3 V +/-0.3 V, V

DD

= 1.8 V +/-0.15 V, T

A

= -40°C to +85°C)

4.10 Schmitt Trigger Characteristics

Vifall

min

Virise

max

Vhyst

min

3.3V

spec (prelimi-

nary)

0.8

2

0.3

1.8V

target spec

0.4

1.3

0.2

4.11 Module and ASIC Code (Chip ID)

The ASIC code (version number of the ASIC) can be read from the ID register in the

SCRB (see 2.3.10.9.1).