Copyright © Siemens AG 2016. All rights reserved

97

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

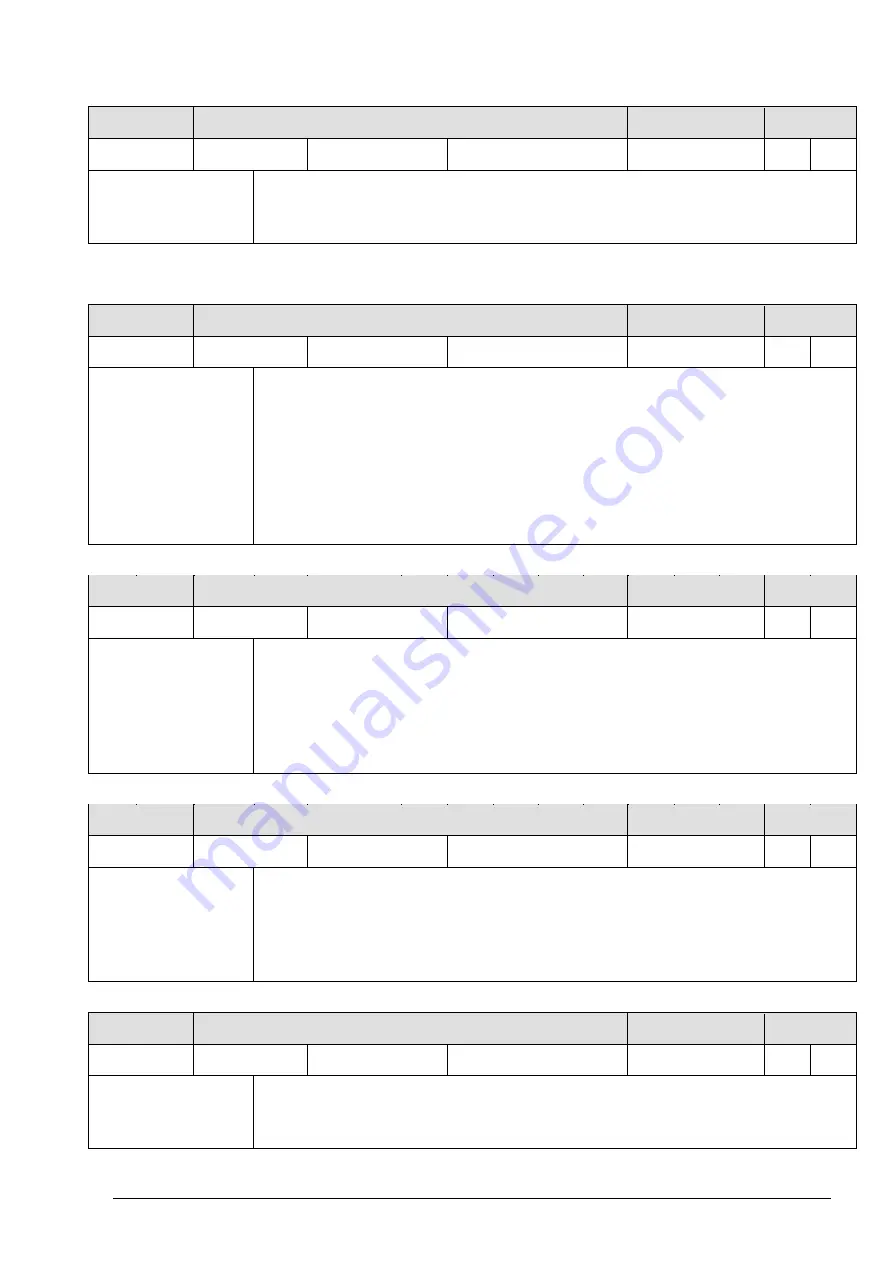

Register:

PRIOREG95

Address:

617Ch

Bits:

6dt0

Reset value:

5Fh

Attributes:

r

w

Description:

Priority Register

Specification of the priority of an interrupt request at the associated

Binary code of the priority input

Module: /icu_ertec_addr_dec_top/icu8_inst

Register:

ID_REGISTER

Address:

8000h

Bits:

15dt0

Reset value:

0006h

Attributes:

r

Description:

Version number of the Interrupt Controller Unit

Version number

1: 128 IR

2: 16 IR, no ZSV error, default vector FFFFFFFFF

3: 32 IR

4: 32 IR, DBG-ACK mask

5: generic ICU

6:ICU core IP

Register:

IRVEC

Address:

8004h

Bits:

2dt0

Reset value:

0h

Attributes:

rh

Description:

Interrupt Vector Register

Number of the highest priority pending Interrupt Request

For pending valid interrupt: binary code of the Interrupt number.

Default vector: 0h

Important: If SW acknowledges the current pending Interrupt Request with

a write access on ACK, the content on IRVEC is also lost.

Register:

ACK

Address:

8008h

Bits:

2dt0

Reset value:

0h

Attributes:

rht

Description:

Interrupt Vector Register with IRQ Acknowledge

Acknowledge the highest priority pending interrupt request by reading the

associated interrupt vector

For valid request: binary code of the input number

Otherwise: Default vector 0h

Register:

IRCLVEC

Address:

800Ch

Bits:

2dt0

Reset value:

0h

Attributes:

wt

Description:

Interrupt Request Clear Vector

Direct clearing of an interrupt request in the Interrupt Request Register

Binary code of the input number of the request to be cleared