Copyright © Siemens AG 2016. All rights reserved

365

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

2.3.10.9 SCRB (System Control Register Block)

This block contains central registers for controlling the ERTEC 200P

.

2.3.10.9.1

Hardware Identifier Register

Contains the identification number of the ERTEC 200P and the target platform

(ASIC/FPGA), and the versioning in ClearCase (ID_REG, ERTEC 200PLUS_TAG).

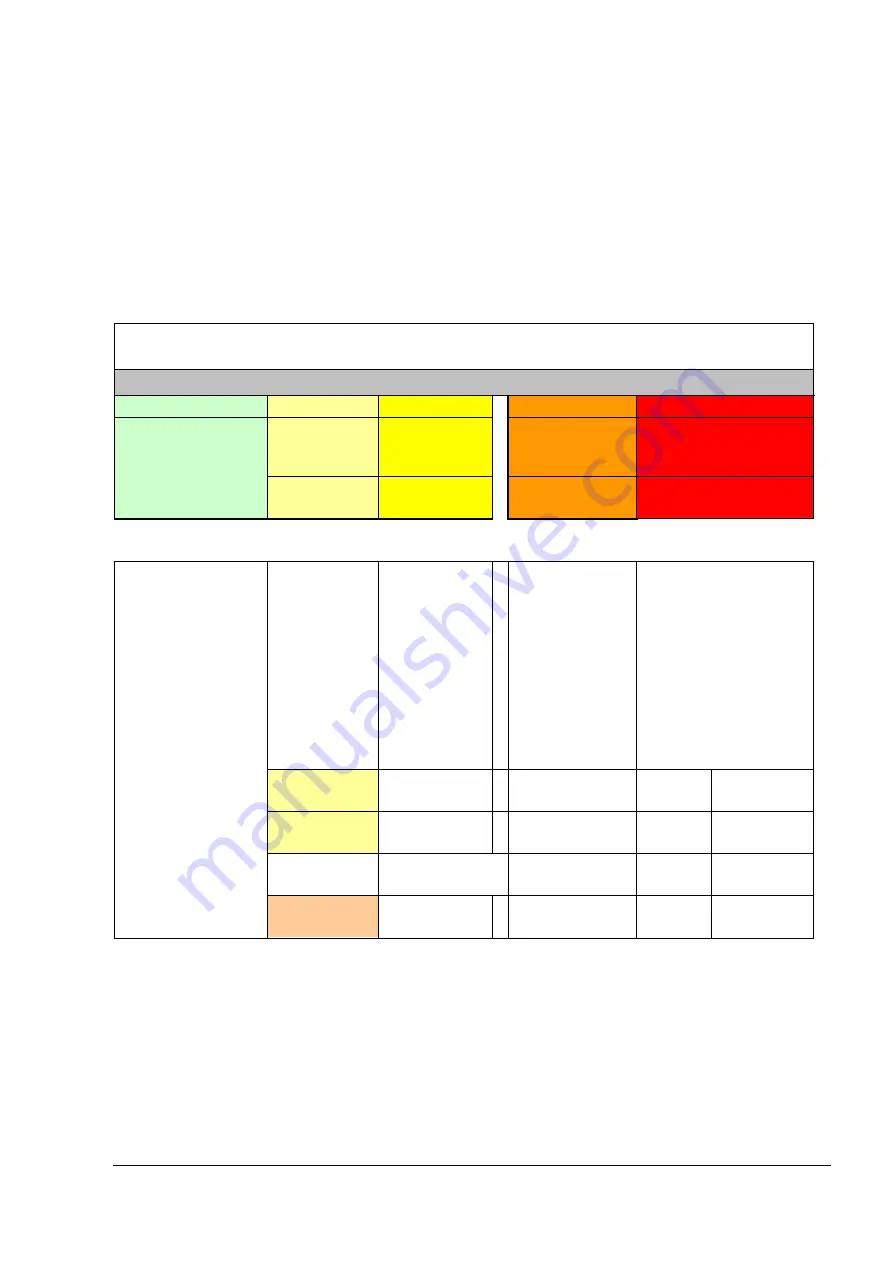

32-bit register

31 .. 21

20 .. 19

18 .. 16

15 .. 11

10 .. 0

11

2

3

5

11

Identification

Target Plat-

form

Patch Label

Increment

R Label

IRTE,ICU,DSA,…

ASIC,FPGA,

….

Gray-coded

ClearCase

increment

ClearCase HDL

label

Unique number

per module,

managed central-

ly in the A&D IP

list.

A number can

consist of a "ma-

jor" and "minor"

number.

For labeling

metal fixes

in the ASIC

flow; only

valid if plat-

form =

ASIC. In-

crement/R

Label is then

invalid

Represents

the HDL in-

crement value

of the Clear-

Case label

Represents the HDL

counter value of the

ClearCase label

00 = ASIC

000 = no

patch yet

01 = FPGA

001 = 1st

patch

10 = re-

served

etc. (Gray-

coded)

11 = user

defined

Table 21:

ERTEC 200P, ID register