Copyright © Siemens AG 2016. All rights reserved

486

ERTEC 200P-2 Manual

Technical data subject to change

Version

1.0

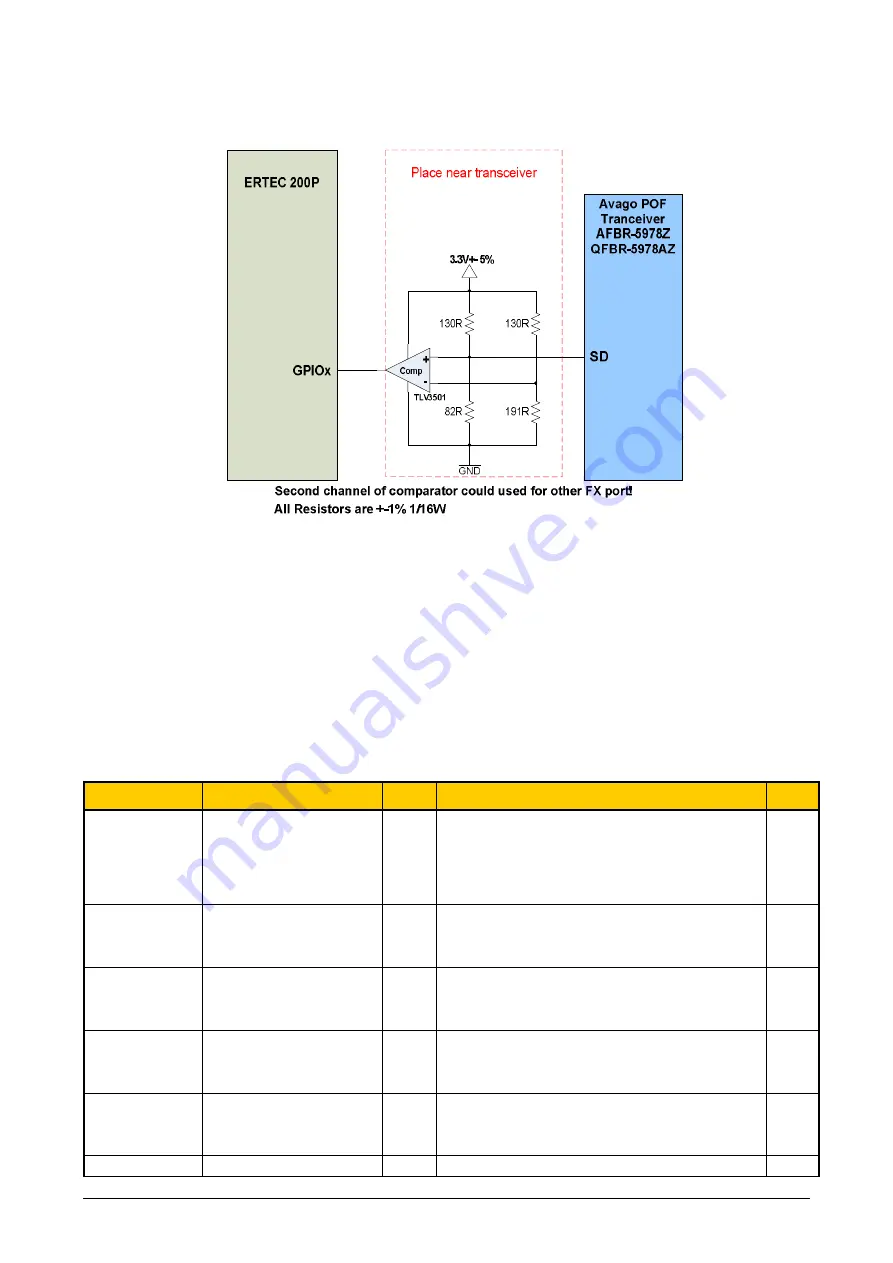

The following level translation circuit is recommended

by using of GPIOs

(see chapter

2.3.10.9.21). Comparator should be placed near transceiver. The 3,3V supply voltage

tolerance for

POF transceiver

is limited to

+- 5%

.

Figure 57: SD level translation circuit

4.7 Wiring of pins not used

The following applies in general:

IN and INOUT pins that do

not

have an internal pull resistor must be connected to

an external pull resistor.

If the internal pull-up/pull-down resistor of the GPIOs is

deactivated

, it must be ac-

tivated with the SW or an external pull-up/pull-down resistor is to be connected.

For wiring PHY pins that are not used, see xxx

Signal

Signal description

Dir

Function description

Ball

ATP

Analog Test Function

out Analog Test

Enable to monitor or drive specific nodes in the

analog circuit during analog test. For debugging

purposes it is recommended to have this pin ac-

cessable for an oscilloscope on a PCB. This pin is

not used in normal operation.

K18

TEST

IC-Test-Mode

in

IC Test Mode

Select signal for ASIC test.

For normal operation this pin must be connected by a

1k Ohm Pull down resistor to GND.

R9

TMC1

Testmode_1

in

Test Mode Control

Signal for ASIC test.

For normal operation this pin must be connected

directly to GND.

F12

TMC2

Testmode_2

in

Test Mode Control

Signal for ASIC test.

For normal operation this pin must be connected

directly to GND.

R14

TACT

TESTACT-TAP-RESET

in

Special Test Mode TAP Controller

Used for Boundary scan test.

For normal operation this pin must be connected by a

1k Ohm Pull down resistor to GND.

R12

TAP_SEL

TAP Select

in

TAP

Select

T7