Copyright © Siemens AG 2016. All rights reserved

489

ERTEC 200P-2 Manual

Technical data subject to change

Version

1.0

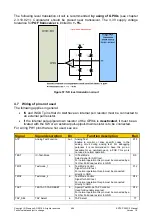

XSRST

XHIF_A19-15

A_PHY_1

A_PHY_2

L_PHY_1

L_PHY_2

REF_CLK

GPIO44:32 XHIF_A13-1

GPIO45

XHIF_A14

1)

Not visible as IO signals at the ASIC, but wired in the interposer of the ASIC package between ERTEC-Die and PHY-

Die

The other pins connected to the Die, CTRL_STBY3-9, control the remaining signal pins

(EMC with 1.8 V; PHY with 3.3 V). These CTRL_STBY pins are not connected to package

balls, but instead fixed to the corresponding VDD in the interposer of the ASIC package.

4.8.3 Power-Up Sequence (PLL)

The standby signal (STBY) to the PLL is an extension of XRESET by ca. 2.5 µsec.

4.8.4 PLL Behavior

4.8.4.1 following crystal break

If the ext. crystal breaks, i.e. CLK_A, CLK_B are

open

clamped to '0'

clamped to '1',

a frequency of 100 MHz … 300 MHz is established at the PLL output (free-running fre-

quency).

4.8.4.2 upon temporary clock failure

The period jitter is considerably less than 50 ps and is therefore within the specified range

provided the recommended filter connections for AVDD decoupling are used.

If the reference clock for the ERTEC 200P PLL fails, the frequency changes continuously

until it reaches the final value after ca. 30 µs.