Copyright © Siemens AG 2010. All rights reserved.

Page

65

ERTEC 400 Manual

Technical data subject to change

Version 1.2.2

Ether-

net

port

0

Buffer

RMII

Ether-

net

port

1

Buffer

RMII

Ether-

net

port

2

Buffer

RMII

Ether-

net

port

3

Buffer

RMII

ERTEC400

RMII Mode

(Interface to 4-port PHY

via RMII)

Ether-

net

port

0

Buffer

MII

Ether-

net

port

1

Buffer

MII

Ether-

net

port

2

Buffer

RMII

Ether-

net

port

3

Buffer

RMII

ERTEC400

MII Mode

(Interface to two 1-port PHYs

via MII)

PHY0

(RMII)

PHY1

(RMII

PHY2

(RMII)

PHY3

(RMII)

PHY0

(MII)

PHY1

(MII)

R

X

_

C

L

K

T

X

_

C

L

K

R

X

_

C

L

K

T

X

_

C

L

K

REF_CLK

(50 MHz)

PHY_CLK

(25 MHz)

Figure 10: Clock Supply of Ethernet Interface

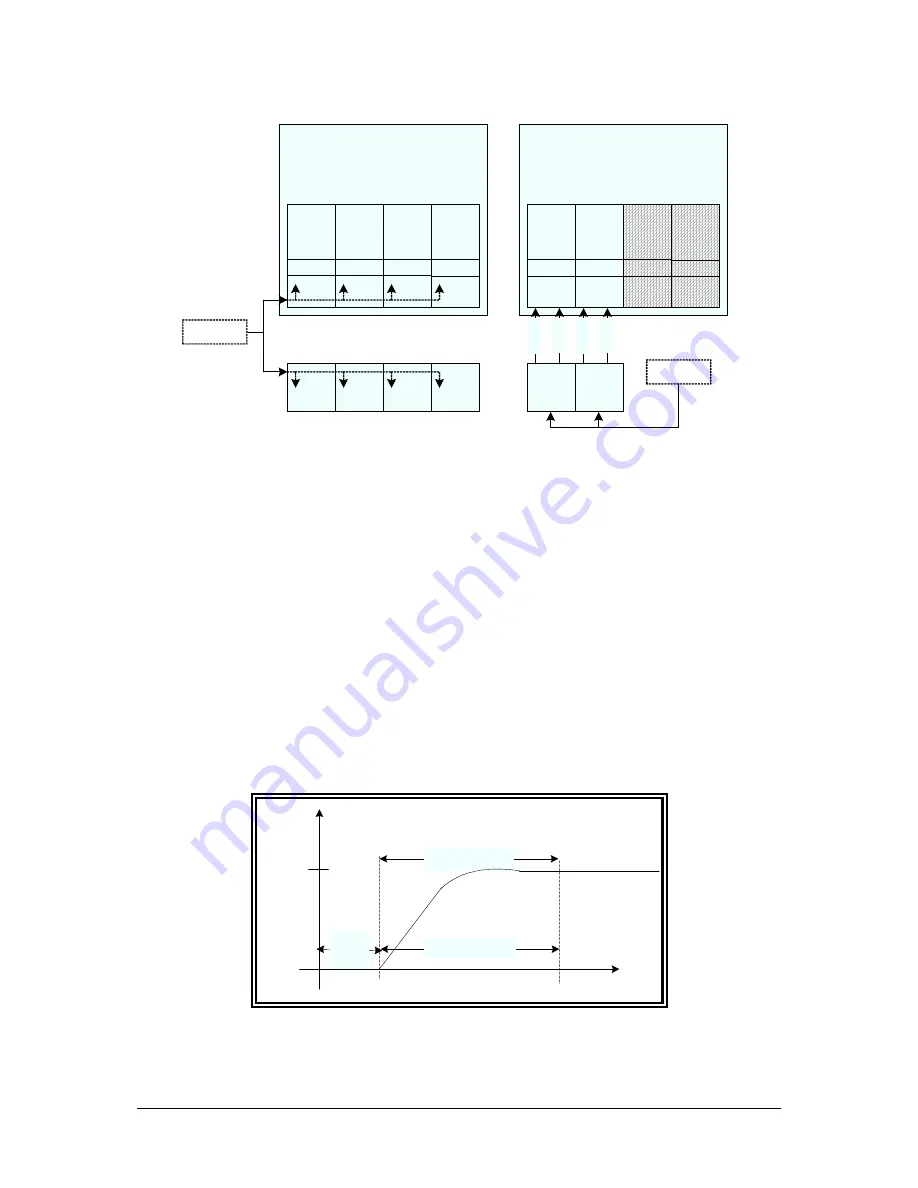

5.2 Reset Logic of the ERTEC 400

The reset logic resets the entire circuit of the ERTEC 400 except for the PCI portion of the AHB-PCI bridge.

The reset system of the ERTEC 400 is enabled by the following events:

•

Hardware reset via external

RESET_N

pin

•

Software reset via

XRES_SOFT

bit in the reset control register

•

Watchdog reset via watchdog timer overflow

The triggering reset event can be read out in the reset status register.

5.2.1

Hardware Reset

The external hardware reset circuitry is connected at the

RESET_N

pin of the ERTEC 400. If the hardware reset

is enabled, the entire ERTEC 400 circuit except for the PCI portion is reset internally. The hardware reset must be

present steadily for

at least 35 µs

(see figure below). Afterwards, the PLL powers up within t

Lock =

400 µs. The

lock status of the PLL is monitored. The state of the PLL can be read out in the

PLL_STAT_REG

status register.

In the case of the hardware reset, a bit is set in the reset status register. This bit remains unaffected by the

triggered reset function. This register can be evaluated after a restart. The following figure shows the power-up

phase of the PLL after a reset.

f/MHz

t/µs

t

LOCK

= 400 µs

35

Power-up PLL

active

Reset

300

Figure 11: Power-Up Phase of the PLL