Copyright © Siemens AG 2010. All rights reserved.

Page

83

ERTEC 400 Manual

Technical data subject to change

Version 1.2.2

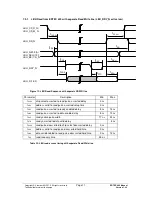

8 PCI Interface

The AHB-PCI bridge of Fujitsu-Siemens is used as the PCI interface. A 2-Gbyte segment starting at address

0x80000000 (offset = 2 Gbytes) is on the AHB bus. See also “Detailed Memory Description“ in Section 9.2. The

configuration area of the PCI macro is addressed here. Mapping of addresses of the AHB to the address area of

the PCI bus can be set in the configuration area. For a description of the PCI bridge, refer to /3/.

The bus system is selected using the CONFIG[2] input pin.

CONFIG[2] = 1 PCI bus system is active

The 32-bit PCI interface operates at a maximum frequency of 66 MHz.

The following signal pins are available for the PCI interface on the ERTEC 400.

•

Data/address bus

32-bit

AD[31 : 0]

•

PCI power management 1

PME_N

•

PCI control cables

11

PAR, FRAME_N, IRDY_N, TRDY_N, DEVSEL_N

STOP_N, IDSEL, PERR_N, REQ_N, GNT_N, M66EN

•

PCI bus clock

1

CLOCK_PCI

•

PCI bus reset

1

RES_PCI_N

•

CS for 4 address spaces 4

CBE0_N – CBE3_N

•

Interrupt outputs

3

INTA_N, INTB_N, SERR_N

8.1 PCI Functionality

The PCI functions are described in general terms in this section.

8.1.1

General Functions of the PCI Interface:

•

Compliant with PCI Specification 2.2

•

Host functionality

•

Master/target interface

•

32-bit AHB interface

•

32-bit PCI interface

•

3.3 V supply (5 V-compatible)

•

Maximum operating frequency of 66 MHz

•

Loading of PCI configuration registers from ARM946 processor

•

2 PCI interrupt outputs (INTA_N and INTB_N)

•

Power Management Version 1.1

•

No

PCI interrupt inputs

•

No

support of lock transfers

8.1.2

PCI Master Interface:

The following accesses are supported:

•

Memory Read

•

Memory Read Line

•

Memory Read Multiple

•

Memory Write Single/Burst

•

Memory Write and Invalidate

•

1 delayed instruction queue

•

Write-data FIFO with a depth of 16

•

Delayed read-data FIFO with a depth of 16

•

Configuration area is loaded from the ARM946 (not from an EPROM)