Copyright © Siemens AG 2010. All rights reserved.

Page

84

ERTEC 400 Manual

Technical data subject to change

Version 1.2.2

8.1.3

PCI Target Interface:

The following accesses are supported:

•

Memory Read

•

Memory Read Line

•

Memory Read Multiple

•

Memory Write

•

Memory Write and Invalidate

•

Configuration Read/Write (Type 0)

•

I/O Read/Write

•

6 ERTEC 400-internal address spaces

•

1 IRT communication function

•

1 delayed instruction queue

•

Write-data FIFO with a depth of 16

•

Delayed read-data FIFO with a depth of 16

•

Configuration area is loaded from the ARM946 (not from an EPROM)

8.1.4

Combination of PCI-master/target operation:

Caution:

Under occasional and unfavorable conditions during permanent operation, a deadlock situation (including data

loss) at the internal AHB bus system can occur.

The following conditions must coincide for this to happen:

1. PCI-bridge is used as PCI-target AND PCI-master.

2. ARM initiates read accesses to the memory of the external host as a PCI-master.

3. External host initiates write accesses to the memory at ERTEC400 EMIF (ERTEC400 as PCI-target).

4. AHB arbiter is set to round-robin-mode, or ARM has the highest priority, when the AHB arbiter is set to fixed-

priority-mode.

The described combination can occur during an ERTEC400 operation, in which acyclic communication data is

exchanged between the ERTEC400 and the memory of an external host via ERTEC400 PCI-master interface. In

this combination, the PROFINET software stack runs on the integrated ARM of ERTEC400.

Workaround:

If the PCI bridge acts as a PCI master, the configuration of AHB arbitration to fixed-priority-mode must be done

using the following procedure. "Bit 3 ARB_MODE" of the "M_LOCK_CTRL" register (address 0x4000264C) must

be set by the 2nd level bootcode.Before this bit is set, you must disable all other AHB masters.

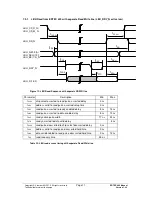

See flowchart: