The baud rate generation is derived from the internal 50 MHz APB clock. The resulting deviations from the standard

baud rates used are so small that a secure data transmission is achieved.

The baud rate is calculated according to the following formula:

F

UARTCLK

F

UARTCLK

BR = -----------------------------

or BAUDDIV = (-----------------------------) - 1

(1) x 16

BR x 16

This yields the following error tolerance calculation:

(BR –BRI)

E

p

= ----------------- x 100%

where BRI is the ideal baud rate

BRI

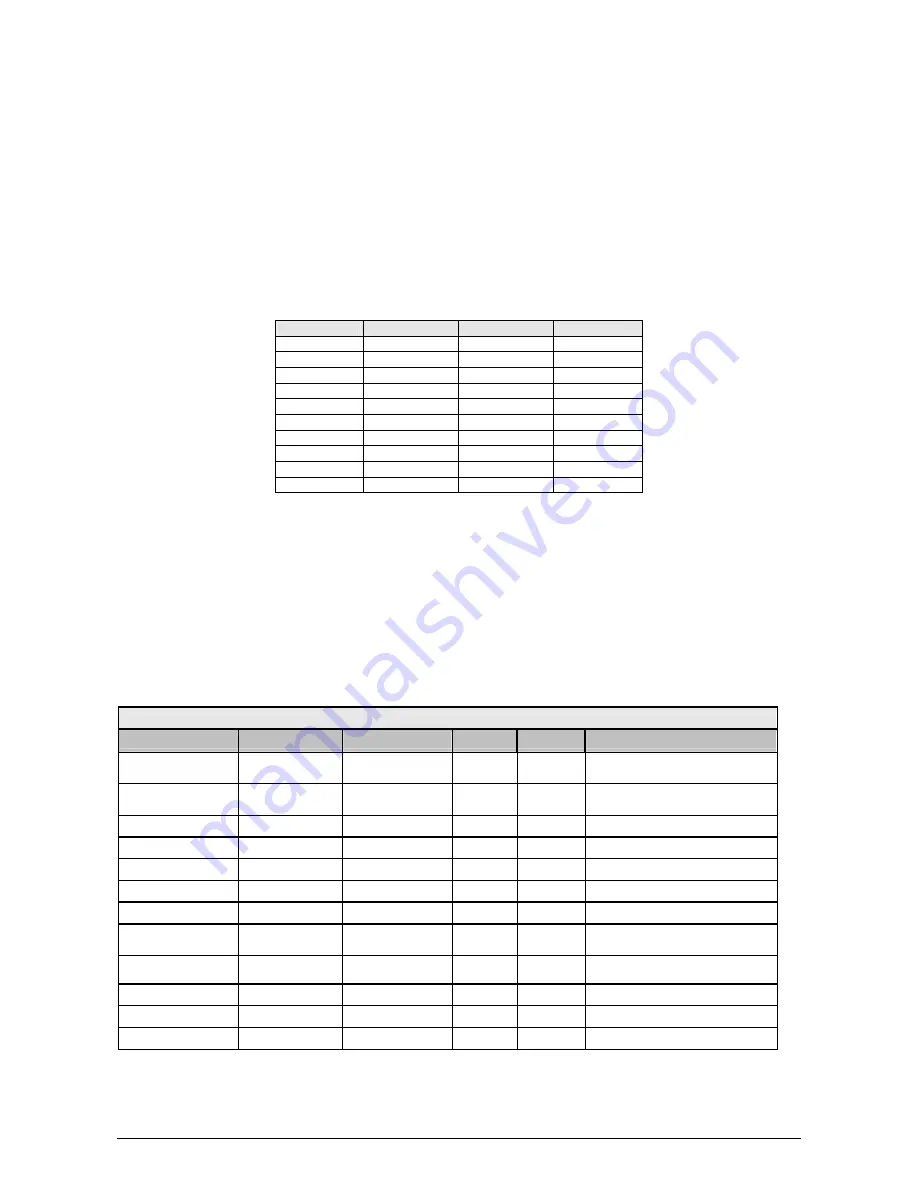

The following table shows the baud rate values to be set and the deviations from the standard baud rates. The

associated error percentages are within the baud rate tolerance range.

BRI

BAUDDIV

BR

E

P

%

115200 26

115740 +0,47

76800 40

76219 -0,76

57600 53

57870 +0,47

38400 80

38580 +0,47

19200 162

19171 -0,15

14400 216

14400.9 +0,006

9600 325

9585.9 -0,15

2400 1301 2400.15

+0,006

1200 2603 1200.077

+0,006

110 28408

110.0004

+0.0003

The UART

from an external PC are to be loaded to the

ERTE

[3:0] inputs during the active reset phase.

The BOOT

g of the program code. The “Boot strap

loader” functio

If the user doe

terface.

4.6.1

The UART

Table 13:

Baud Rates for UART at F

UARTCLK

=50 MHz

can also be used as a BOOT medium if, for example, functions

C 200 and executed. The BOOT medium is selected by the BOOT

loader then takes over setting of the UART signal pins and loadin

nality is also used.

s not utilize the UART, it can also be used as a debugging in

Address Assignment of UART Registers

registers are

8 bits in width

.

UART

(Start 0x4000_2300)

Register Name

Offset Address

Address Area

Access

Default

Description

UARTDR

0x0000

1 bytes

R/W

0x--

Read/write data from interface

UARTRSR/UARTECR 0x0004

1

bytes

R/W 0x00

Receive status register (read)

Error clear register (write)

UARTLCR_H

0x0008

1 bytes

R/W

0x00

Line control register high byte

UARTLCR_M

0x000C

1 bytes

R/W

0x00

Line control register middle byte

UARTLCR_L

0x0010

1 bytes

R/W

0x00

Line control register low byte

UARTCR

0x0014

1 bytes

R/W

0x00

Control register

UARTFR

0x0018

1 bytes

R

0x9-

Flag register

UARTIIR/UARTICR 0x001C

1

bytes

R/W 0x00

Int identification register (read)

Interrupt clear register (write)

UARTILPR 0x0020 1

bytes

R/W

0x00

IrDA Low Power Counter Register

(not supported in the ERTEC200)

0x0024 - 0x003C

Reserved

0x0040 - 0x0098

Reserved for test purposes

0x009C - 0x00FF

Reserved for future extension

Table 14: Overview of UART Registers

Copyright © Siemens AG 2007. All rights reserved.

49

ERTEC 200 Manual

Technical data subject to change

Version 1.1.0