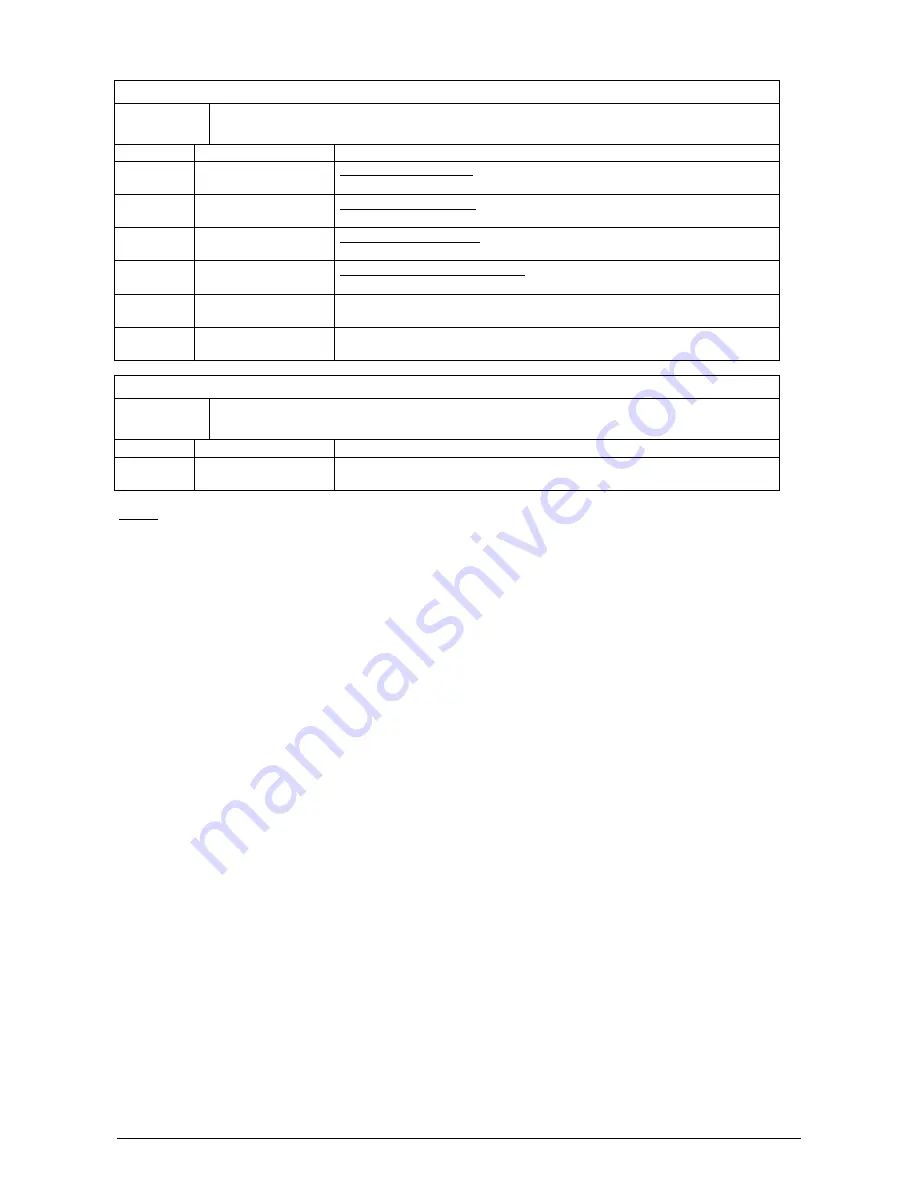

UARTIIR/UARTICR

R/W

Addr.: 0x4000_231C Default: 0x00

Description

UART interrupt identification register (read)

UART interrupt clear register (write)

Bit No.

Name

Description

0

MIS (Read)

Modem Interrupt Status This bit is set if UARTMSINTR is active.

1

RIS (Read)

Receive Interrupt Status This bit is set if UARTRXINTR is active.

2

TIS (Read)

Transmit Interrupt Status This bit is set if UARTTXINTR is active.

3

RTIS (Read)

Receive Timeout Interrupt Status This bit is set if UARTRTINTR is active.

7 – 4

----- (Read)

Reserved

Value is undefined

7 – 0

----- (Write)

Writing to this register deletes the MIS bit irrespective of the value written.

UARTILPR

R/W

Addr.: 0x4000_2320 Default: 0x00

Description

UART IrDA low power counter registers

(not supported in the ERTEC 200)

Bit No.

Name

Description

7 – 0

ILPDVSR

8-bit low power divisor value

NOTE: The low power divisor is calculated according to the following formula:

F

UARTCLK

ILPDVSR

= ---------------------- - 1

FIrLPBAUD16 is nominally 1.8432 MHz

F

IrLPBAUD16

Zero is not a valid divisor.

Copyright © Siemens AG 2007. All rights reserved.

53

ERTEC 200 Manual

Technical data subject to change

Version 1.1.0