5

General Hardware Functions

5.1 Clock Generation and Clock Supply

The clock system of the ERTEC 200 basically consists of four clock systems that are decoupled through asynchronous

transfers.

This includes the following clock systems:

•

ARM946E-S together with AHB bus, APB bus, and IRT

•

LBU

•

JTAG

Interface

•

PHYs and Ethernet MACs

5.1.1

Clock Supply in ERTEC 200

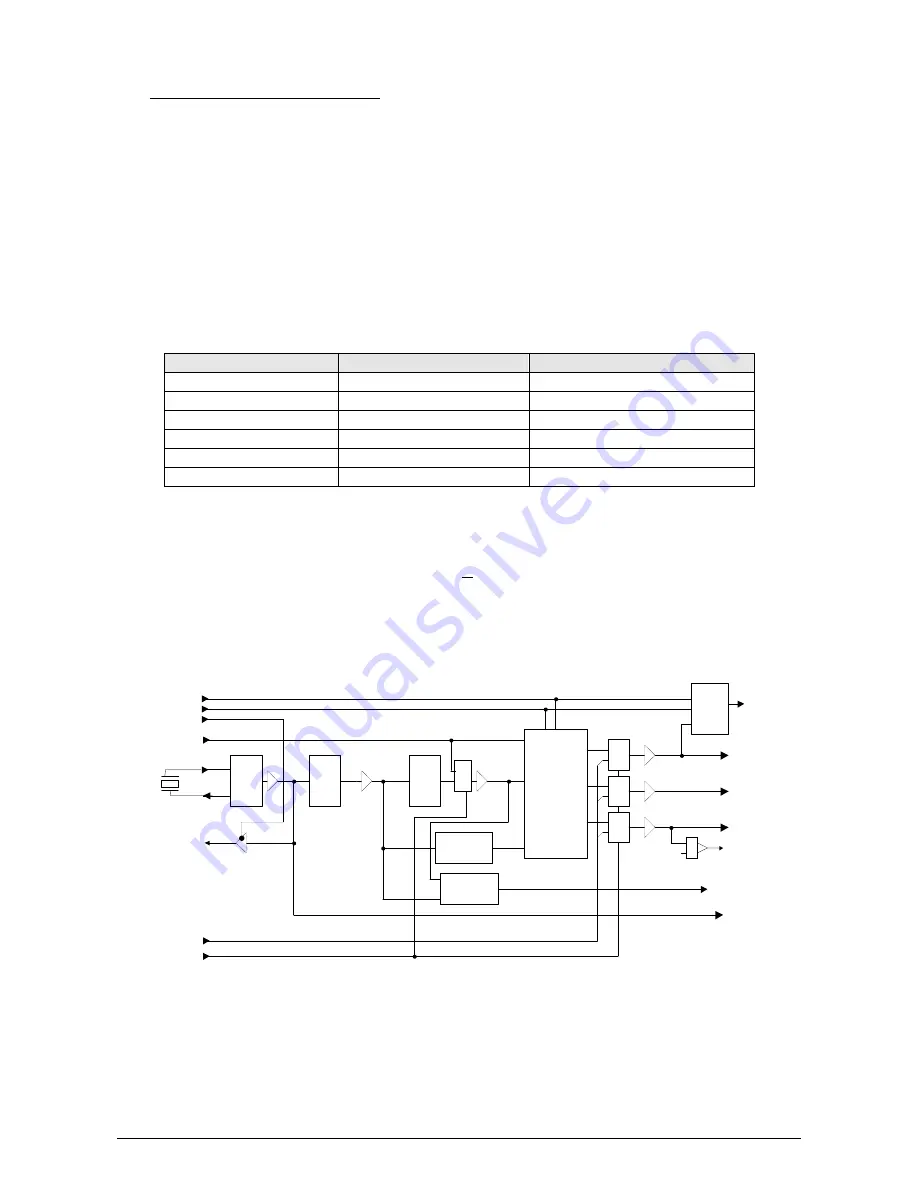

The required clocks are generated in the ERTEC 200 by means of internal PLL and/or through direct infeed.

The following table provides a detailed list of the clocks:

MODULE

CLOCK SOURCE

FREQUENCY

ARM946ES PLL

50/100/150

MHz

(scalable)

AHB/EMIF/ICU/LBU PLL

50

MHz

IRTE (except MAC-MII)

PLL

50/100 MHz

APB PLL 50

MHz

JTAG JTAG-Clock 0-10

MHz

MAC-MII/PHY CLKP_A

25

MHz

Table 17: Overview of ERTEC 200 Clocks

A PLL is integrated to generate the internal clocks in the ERTEC 200. The clock supply of the PLL takes place via the

following input pins:

¾

25 MHz quartz at the inputs

CLKP_A

and

CLKP_B

or

¾

25 MHz clock generator at input

CLKP_A

The input clock is divided down by a factor of 12.5 MHz and fed into the PLL. The PLL generates a clock of 300 MHz,

which supplies the following clock generator. This generates all system clock required for the ERTEC 200.

The following figure shows the generation of the ERTEC 200 clocks:

Divider

1:2

REF_CLK

25 MHz

CONFIG1

APLL

PLL_IN

(12,5 MHz)

PLL_OUT

(300 MHz)

CONFIG4

CONFIG3

MUX

MUX

MUX

SCANMODE

CLK_ARM

CLK_100

CLK_50

HCLKEN -

Gen.

HCLKEN

(ARM9)

Lock -Timer

Power -

up

(650us)

Loc

k

CLK_IN

Enable

PLL_LOCK_STATE

BYPASS_CLK_IN

Clock

Generation

0

1

0

1

0

1

OS

C

MUX

SCAN_CLK(2:0)

2

0

1

BYPASS_CLK

100MHz

Lock

Monitor

PHY_CLK

&

&

CLK_UART

CLKP_A

25

MHz

CLKP_B

Figure 9: Clock Generation in ERTEC 200

Synchronous clocks CLK_50MHz and CLK_100MHz are used primarily in the ERTEC 200. For the ARM946E-S

processor, the required processor clock can be set via the configuration pins

CONFIG[4:3]

:

¾

CONFIG4, CONFIG3 = 00

Æ

ARM946 processor clock is 50 MHz.

¾

CONFIG4, CONFIG3 = 01

Æ

ARM946 processor clock is 100 MHz.

¾

CONFIG4, CONFIG3 = 10

Æ

ARM946 processor clock is 150 MHz.

¾

CONFIG4, CONFIG3 = 11

Æ

Reserved

Copyright © Siemens AG 2007. All rights reserved.

64

ERTEC 200 Manual

Technical data subject to change

Version 1.1.0