6.1 Address Assignment of EMIF Registers

The EMIF registers are

32 bits in width

. These registers can only be written to with double words.

EMIF

(Base Address 0x7000_0000)

Register Name

Offset Address

Address Area

Access

Default

Description

Revision_Code_and

_Status

0x0000

4 bytes

R

0x00000100

Revision code and status register

Async_Wait_Cycle

_Config

0x0004

4 bytes

W/R

0x40000080

Async wait cycle config register

SDRAM_Bank_

Config

0x0008

4 bytes

W/R

0x000020A0

SDRAM bank config register

SDRAM_Refresh

_Control

0x000C 4

bytes

W/R

0x00000190

Setting of refresh rate

Indication for timeout

Async_BANK0_

Config

0x0010 4

bytes

W/R

0x3FFFFFF2

Timing/data bus width for access

via async. interface CS_PER0_N

Async_BANK1_

Config

0x0014 4

bytes

W/R

0x3FFFFFF2

Timing/data bus width for access

via async. interface CS_PER1_N

Async_BANK2_

Config

0x0018 4

bytes

W/R

0x3FFFFFF2

Timing/data bus width for access

via async. interface CS_PER2_N

Async_BANK3_

Config

0x001C 4

bytes

W/R

0x3FFFFFF2

Timing/data bus width for access

via async. interface CS_PER3_N

Extended_Config

0x0020

4 bytes

W/R

0x03030000

Setting of additional functionalities

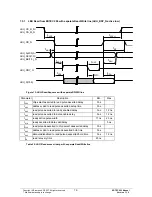

Table 19: Overview of EMIF Registers

6.2 EMIF Register Description

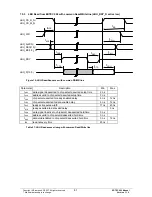

Revision Code and Status

R

Addr.: 0x7000_0000 Default: 0x0000_0100

Description

Revision code and status register

Bit No.

Name

Description

31..16 Reserved

Reserved

15..8 MAJOR_REVISION

01h

7..0 MINOR_REVISION

00h

Async wait cycle config

W/R

Addr.: 0x7000_0004 Default: 0x4000_0080

Description Async

wait

cycle config register

Bit No.

Name

Description

31 Reserved

Reserved

30 WP

Wait

polarity

0: Wait if RDY_PER_N = 0

1: Wait if RDY_PER_N = 1

29..8 Reserved

Reserved

7..0

MAX_EXT_WAIT

This value multiplied by 16 is equivalent to the number of AHB clock cycles

that the async. controller waits for RDY_PER_N before access is terminated

with timeout IRQ.

Copyright © Siemens AG 2007. All rights reserved.

70

ERTEC 200 Manual

Technical data subject to change

Version 1.1.0