STEP 5 Operations

S5-95F

8.3.2

Load and Transfer Operations

Use these load and transfer operations to address the entire program memory of the programmable

controller. They are used mainly for data exchange between the accumulator and memory locations

that cannot be addressed by operands. Table 8-27 provides an overview of the load and transfer

operations.

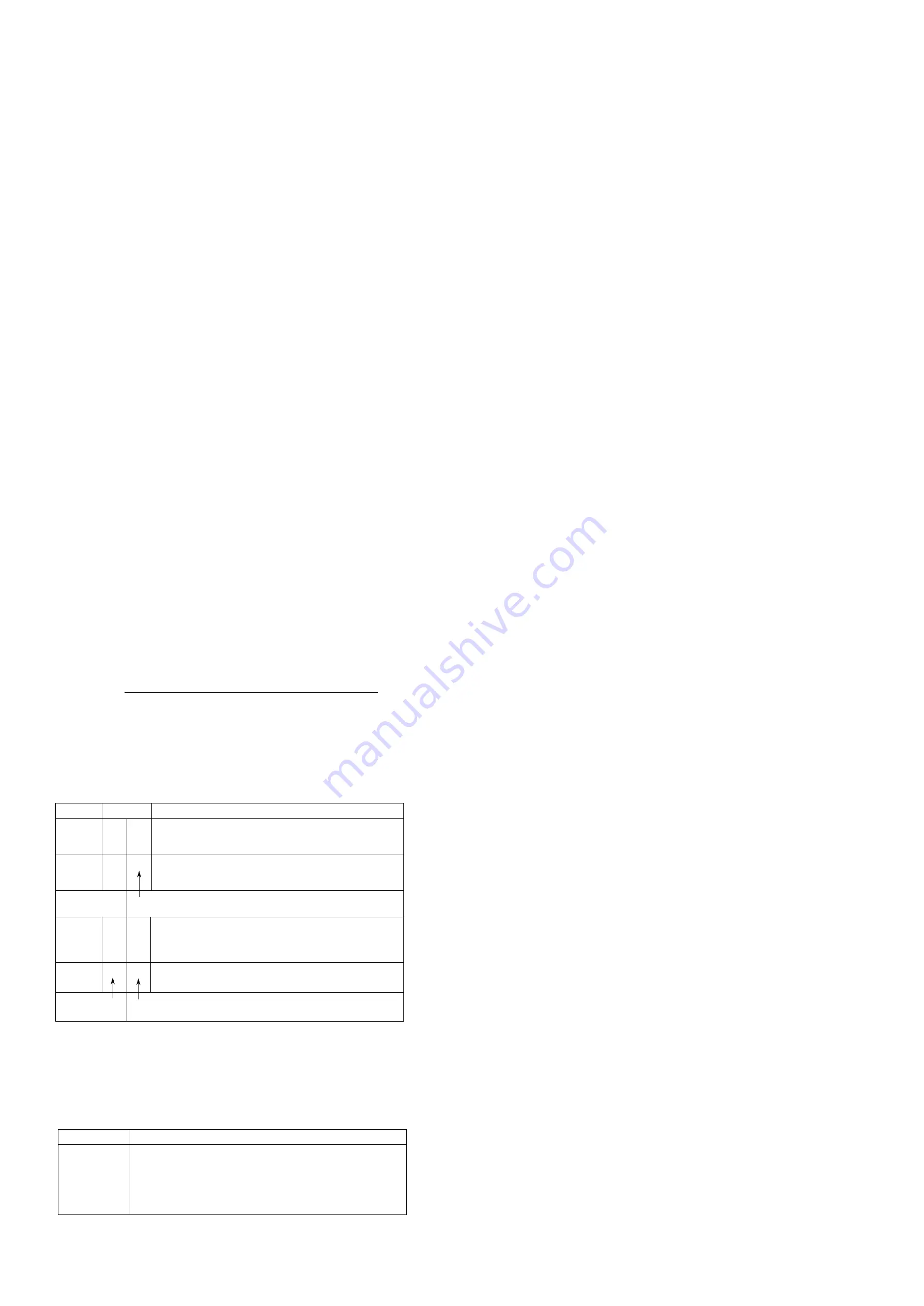

Table 8-27. Overview of Load and Transfer Operations

Operation

Meaning

Operand

LIR

Load the register indirectly

The contents of a memory word are loaded into the specified

register (ACCU 1, 2). The address is in ACCU 1.

TIR

Transfer the register indirectly

The contents of the indicated register are transferred to a memory

location. The address is in ACCU 1.

Parameter

0 (for ACCU 1), 2 (for ACCU 2)

TNB

Transfer a data field (byte-by-byte)

A memory area is transferred in the program memory as a field.

End address destination area:

ACCU 1

End address source area:

ACCU 2

T

Transfer

A word is transferred to the system data area.

Parameter

0 to 255

ID

RS

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

Loading and Transferring Register Contents

Both accumulators can be addressed as registers. Each register is 16 bits wide. Since the "LIR"

and "TIR" operations transmit data by words, the registers are addressed in pairs.

Loading and transferring register contents are independent of the RLO. The processor goes to

ACCU 1 to get the address of the memory location referenced during data exchange. Conse-

quently, make sure that the desired address is stored in ACCU 1 before this system operation is

processed.

Explanation

STL

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a a

.

.

L

KH

F100

LIR

0

Load the address 6100

H

into ACCU 1.

Load the information from the memory location with the address 6100

H

into

ACCU 1.

8-64

EWA 4NEB 812 6210-02