[logikdia-ueberspgschutz-u2-spggegsys-wlk-280802, 1, en_GB]

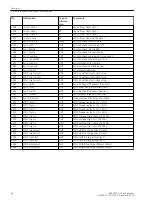

Figure 2-27

Logic diagram of the overvoltage protection for the negative sequence voltage system U

2

The overvoltage protection for the negative sequence system can also be blocked via a binary input

>U2>(>)

BLK

. The stages of the negative sequence voltage protection are automatically blocked as soon as an asym-

metrical voltage failure was detected (“Fuse-Failure-Monitor”, also see Section

for voltage transformers has been signalled via the binary input

>FAIL:Feeder VT

.

During the single-pole dead time, the stages of the negative-sequence overvoltage protection are automati-

cally blocked since the occurring negative sequence values are only influenced by the asymmetrical power

flow, not by the fault in the system. If the device cooperates with an external automatic reclosure function, or

if a singlepole tripping can be triggered by a different protection system (working in parallel), the overvoltage

protection for the negative sequence system must be blocked via a binary input during single-pole tripping.

Please bear in mind that the device is designed for a three-phase voltage connection. Single-phase connection

is also possible but no adjustments have been made in this respect. This must be taken into consideration

when setting the pickup value.

Overvoltage zero-sequence system 3U

0

depicts the logic diagram of the zero-sequence voltage stage. The fundamental component is

numerically filtered from the measuring voltage so that the harmonics or transient voltage peaks remain

largely eliminated.

The triple zero-sequence voltage 3·U

0

is fed to the two threshold stages

3U0>

(address 3722) and

3U0>>

(address 3724). Combined with the associated time delays

T 3U0>

(address 3723) and

T 3U0>>

(address

3725), these stages form a two-stage overvoltage protection for the zero-sequence system. Here too, the

dropout to pickup ratio can be set (

3U0>(>) RESET

, address

3U0>(>) RESET

). Furthermore, a restraint

delay can be configured which is implemented by repeated measuring (approx. 3 periods).

The overvoltage protection for the zero-sequence system can also be blocked via a binary input

>3U0>(>)

BLK

. The stages of the zero-sequence voltage protection are automatically blocked as soon as an asymmetrical

voltage failure was detected (“Fuse-Failure-Monitor”, also see Section

Functions

2.5 Under and over-voltage protection (optional)

100

SIPROTEC 4, 7VK61, Manual

C53000-G1176-C159-5, Edition 05.2018

Summary of Contents for SIPROTEC 4 7VK61

Page 8: ...8 SIPROTEC 4 7VK61 Manual C53000 G1176 C159 5 Edition 05 2018 ...

Page 10: ...10 SIPROTEC 4 7VK61 Manual C53000 G1176 C159 5 Edition 05 2018 ...

Page 16: ...16 SIPROTEC 4 7VK61 Manual C53000 G1176 C159 5 Edition 05 2018 ...

Page 176: ...176 SIPROTEC 4 7VK61 Manual C53000 G1176 C159 5 Edition 05 2018 ...

Page 224: ...224 SIPROTEC 4 7VK61 Manual C53000 G1176 C159 5 Edition 05 2018 ...

Page 264: ...264 SIPROTEC 4 7VK61 Manual C53000 G1176 C159 5 Edition 05 2018 ...

Page 270: ...270 SIPROTEC 4 7VK61 Manual C53000 G1176 C159 5 Edition 05 2018 ...

Page 276: ...276 SIPROTEC 4 7VK61 Manual C53000 G1176 C159 5 Edition 05 2018 ...

Page 346: ...346 SIPROTEC 4 7VK61 Manual C53000 G1176 C159 5 Edition 05 2018 ...