SPC3

PROFIBUS Interface Center

SPC3 Hardware Description

V1.3

Page 43

Copyright (C) Siemens AG 2003 All rights reserved.

2003/04

7.1.6 Interface Signals

The data bus outputs are high-resistance during the reset phase. All outputs are switched to high-resistance

in the test mode. (See block test.)

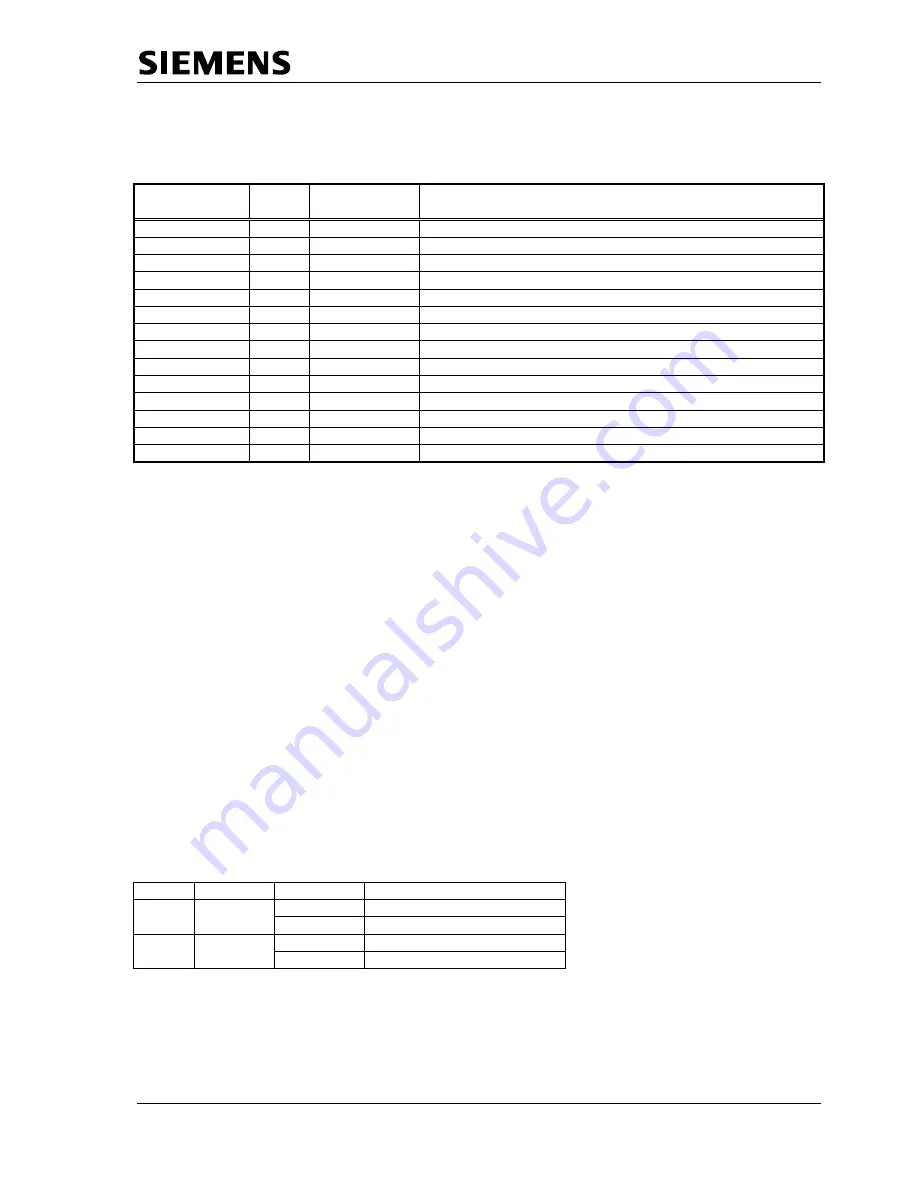

Name

Input/

Output

Type

Comments

DB(7..0)

I/O

Tristate

High-resistance for RESET

AB(10..0)

I

AB(10) has a pull down resistor.

MODE

I

Setting: syn/async interface

XWR/E_CLOCK I

Intel: Write /Motorola: E-Clk

XRD/R_W

I

Intel: Read /Motorola: Read/Write

XCS

I

Chip Select

ALE/AS

I

Intel/Motorola: Address Latch Enable

DIVIDER

I

Scaling factor 2/4 for CLKOUT 2/4

X/INT

O

Tristate

Polarity programmable

XRDY/XDTACK O

Tristate

Intel/Motorola: Ready-Signal

CLK

I

48 MHz

XINT/MOT

I

Setting: Intel/Motorola

CLKOUT2/4

O

Tristate

24/12 MHz

RESET

I

Schmitt-Trigger Minimum of 4 clock pulse cycles

Figure 7.2: Microprocessor Bus Signals

7.2 UART

The transmitter converts the parallel data structure into a serial data flow. Request-to-Send (RTS) is

generated before the first character. The XCTS input is available for connecting a modem. After RTS

active, the transmitter must hold back the first telegram character until the XCTS modem activates.

The receiver converts the serial data flow into the parallel data structure. The receiver scans the serial data

flow with the four-fold transmission speed. Stop bit testing can be switched off for test purposes

(„DIS_STOP_CONTROL = 1“, in mode register 0 or ‘Set_Param-Telegram’ for DP). One requirement of the

PROFIBUS protocol is that no rest states are permitted between the telegram characters. The SPC3

transmitter ensures that this specification is maintained. This following start bit test is switched off with the

parameter setting „DIS_START_CONTROL = 1“ (in mode register 0 or ‘Set_Param telegram’ for DP).

Specified by the four-fold scan, a maximum distortion of the serial input signal of X = -47% to y = +22% is

permissible.

7.3 ASIC Test

All output pins and I/O pins can be switched in the high-resistance state via the XTESTO test pin. An

additional XTEST1 input is provided (more information upon request) to test the block internally with test

automatic devices (not in the target hardware environment!).

Pin No. Name

Function

34

XTEST0

VSS (GND) All outputs high-resistance

VDD (+5V)

Normal SPC3 function

35

XTEST1

VSS (GND) Various test modes

VDD (+5V)

Normal SPC3 function

Figure 7.3: Test Support

XTEST0 and XTEST1 must be placed on V

DD

(+5V) via external pull-up resistors.

Summary of Contents for SPC3

Page 1: ...SIMATIC NET SPC3 Siemens PROFIBUS Controller Hardware Description Date 2003 04 09 ...

Page 2: ......

Page 67: ......