Summary of Contents for E300

Page 1: ...SiFive E300 Platform Reference Manual Version 1 0 1 c SiFive Inc ...

Page 2: ...2 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 4: ...ii SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 12: ...4 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 14: ...6 SiFive E300 Platform Reference Manual Version 1 0 1 ...

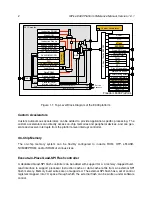

Page 22: ...14 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 32: ...24 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 40: ...32 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 56: ...48 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 60: ...52 SiFive E300 Platform Reference Manual Version 1 0 1 ...