31

Reserved

19.5

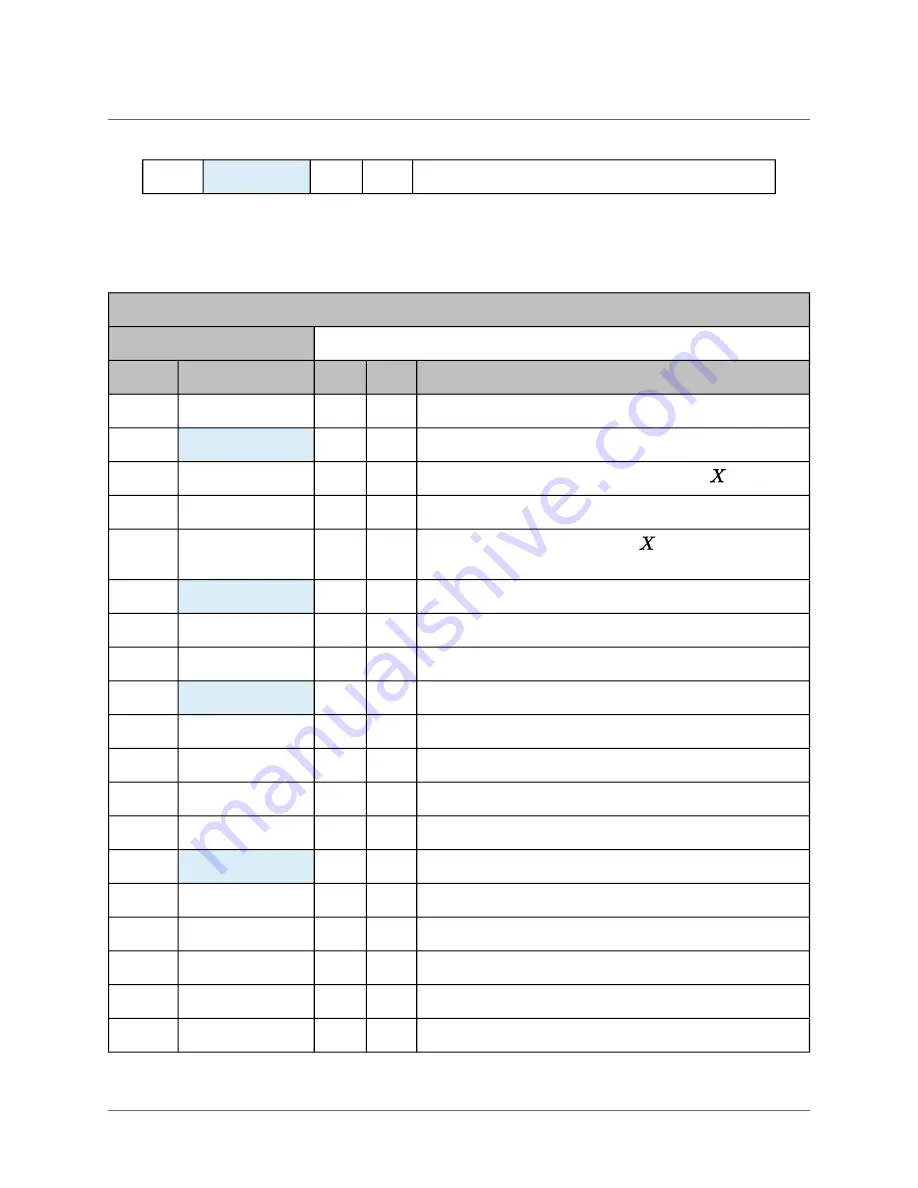

PWM Configuration Register (

pwmcfg

)

PWM Configuration Register (

pwmcfg

)

Register Offset

0x0

Bits

Field Name

Attr.

Rst.

Description

[3:0]

pwmscale

RW

X

PWM Counter scale

[7:4]

Reserved

8

pwmsticky

RW

X

PWM Sticky - disallow clearing

pwmcmp

ip

bits

9

pwmzerocmp

RW

X

PWM Zero - counter resets to zero after match

10

pwmdeglitch

RW

X

PWM Deglitch - latch

pwmcmp

ip

within same

cycle

11

Reserved

12

pwmenalways

RW

0x0

PWM enable always - run continuously

13

pwmenoneshot

RW

0x0

PWM enable one shot - run one cycle

[15:14]

Reserved

16

pwmcmp0center

RW

X

PWM0 Compare Center

17

pwmcmp1center

RW

X

PWM1 Compare Center

18

pwmcmp2center

RW

X

PWM2 Compare Center

19

pwmcmp3center

RW

X

PWM3 Compare Center

[23:20]

Reserved

24

pwmcmp0gang

RW

X

PWM0/PWM1 Compare Gang

25

pwmcmp1gang

RW

X

PWM1/PWM2 Compare Gang

26

pwmcmp2gang

RW

X

PWM2/PWM3 Compare Gang

27

pwmcmp3gang

RW

X

PWM3/PWM0 Compare Gang

28

pwmcmp0ip

RW

X

PWM0 Interrupt Pending

Table 84:

PWM Count Register

Table 85:

PWM Configuration Register

Chapter 19 Pulse Width Modulator (PWM)

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 97