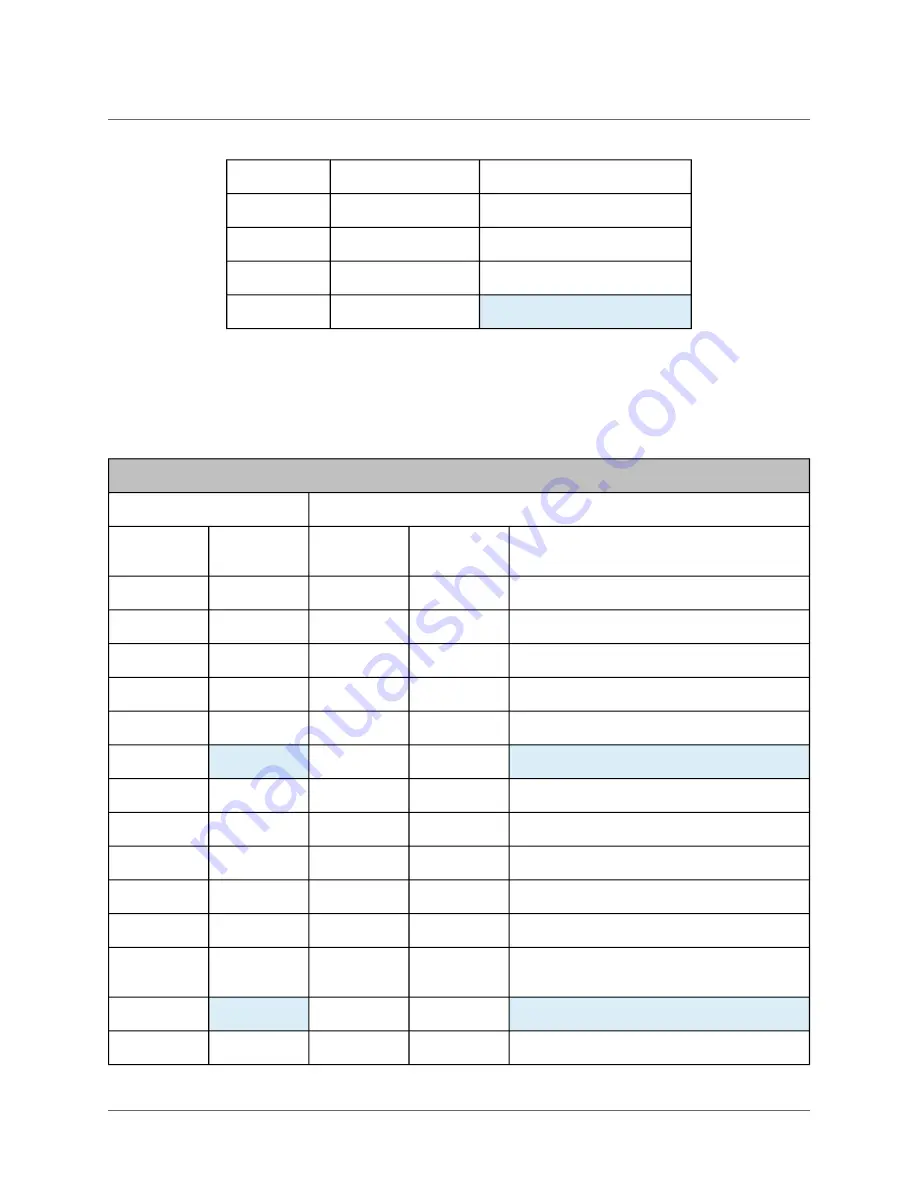

Table 97:

TDR CSRs when used as Breakpoints

CSR Name

Breakpoint Alias

Description

tselect

tselect

Breakpoint selection index

tdata1

mcontrol

Breakpoint match control

tdata2

maddress

Breakpoint match address

tdata3

N/A

Reserved

20.2.1

Breakpoint Match Control Register

mcontrol

Each breakpoint control register is a read/write register laid out in Table 98.

Table 98:

Test and Debug Data Register 3

Breakpoint Control Register (

mcontrol

)

Register Offset

CSR

Bits

Field

Name

Attr.

Rst.

Description

0

R

WARL

X

Address match on LOAD

1

W

WARL

X

Address match on STORE

2

X

WARL

X

Address match on Instruction FETCH

3

U

WARL

X

Address match on User Mode

4

S

WARL

X

Address match on Supervisor Mode

5

Reserved

WPRI

X

Reserved

6

M

WARL

X

Address match on Machine Mode

[10:7]

match

WARL

X

Breakpoint Address Match type

11

chain

WARL

0

Chain adjacent conditions.

[17:12]

action

WARL

0

Breakpoint action to take. 0 or 1.

18

timing

WARL

0

Timing of the breakpoint. Always 0.

19

select

WARL

0

Perform match on address or data.

Always 0.

20

Reserved

WPRI

X

Reserved

[26:21]

maskmax

RO

4

Largest supported NAPOT range

Chapter 20 Debug

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 107