SiFive FE310-G000 Manual

Proprietary Notice

Copyright © 2016–2021, SiFive Inc. All rights reserved.

SiFive FE310-G000 Manual by SiFive, Inc. is licensed under Attribution-NonCommercial-

NoDerivatives 4.0 International. To view a copy of this license, visit http://creativecommons.org/

licenses/by-nc-nd/4.0

Information in this document is provided “as is,” with all faults.

SiFive expressly disclaims all warranties, representations, and conditions of any kind, whether

express or implied, including, but not limited to, the implied warranties or conditions of mer-

chantability, fitness for a particular purpose and non-infringement.

SiFive does not assume any liability rising out of the application or use of any product or circuit,

and specifically disclaims any and all liability, including without limitation indirect, incidental, spe-

cial, exemplary, or consequential damages.

SiFive reserves the right to make changes without further notice to any products herein.

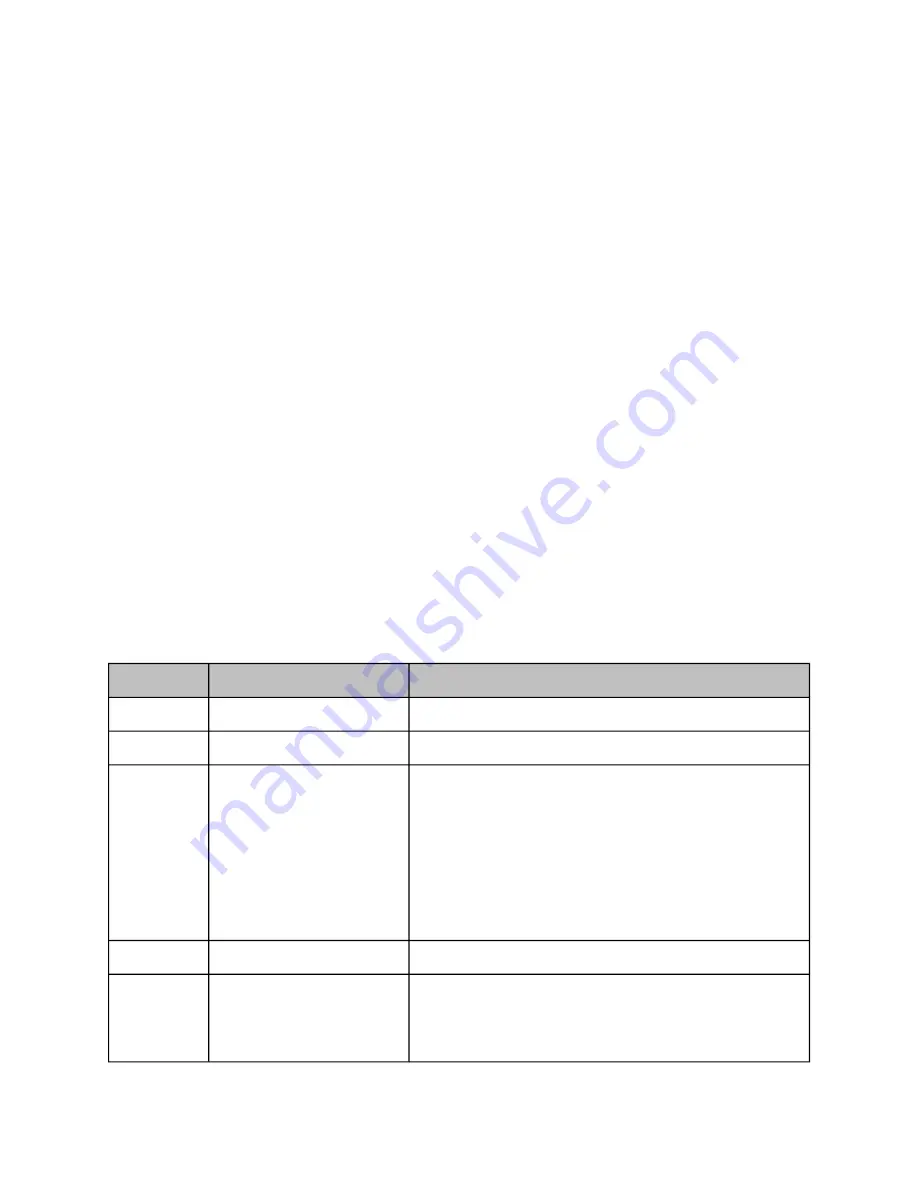

Release Information

Version

Date

Changes

v3p2

March 25, 2021

• Added Creative Commons license

v3p1

August 22, 2019

• Fixed minor error in memory map table

v3p0

January 21, 2019

• Updated formatting and chapter organization to

match newer documents

• Fixed minor error in PLIC interrupt priorities

memory map table

• Added section on performance monitoring

• Removed chapter on Config String, which is

now a deprecated standard

v2p3

October 11, 2017

Core Complex branding

v2p2

September 28, 2017

• Clarify PLIC, PMU, RTC, WDT reset values.

• Add “empty” bit to UART rxdata register map.

• General Formatting.