[5:0]

lfroscdiv

RW

0x4

Ring Oscillator Divider Register

[15:6]

Reserved

[20:16]

lfrosctrim

RW

0x10

Ring Oscillator Trim Register

[29:21]

Reserved

30

lfroscen

RW

0x1

Ring Oscillator Enable

31

lfroscrdy

RO

X

Ring Oscillator Ready

6.8

Alternate Low-Frequency Clock (LFALTCLK)

An external low-frequency clock can be driven on the

psdlfaltclk

pad, when the

psdlfaltclksel

is tied low. This mux selection can only be controlled by external pads, it is not

controllable by software.

6.9

Clock Summary

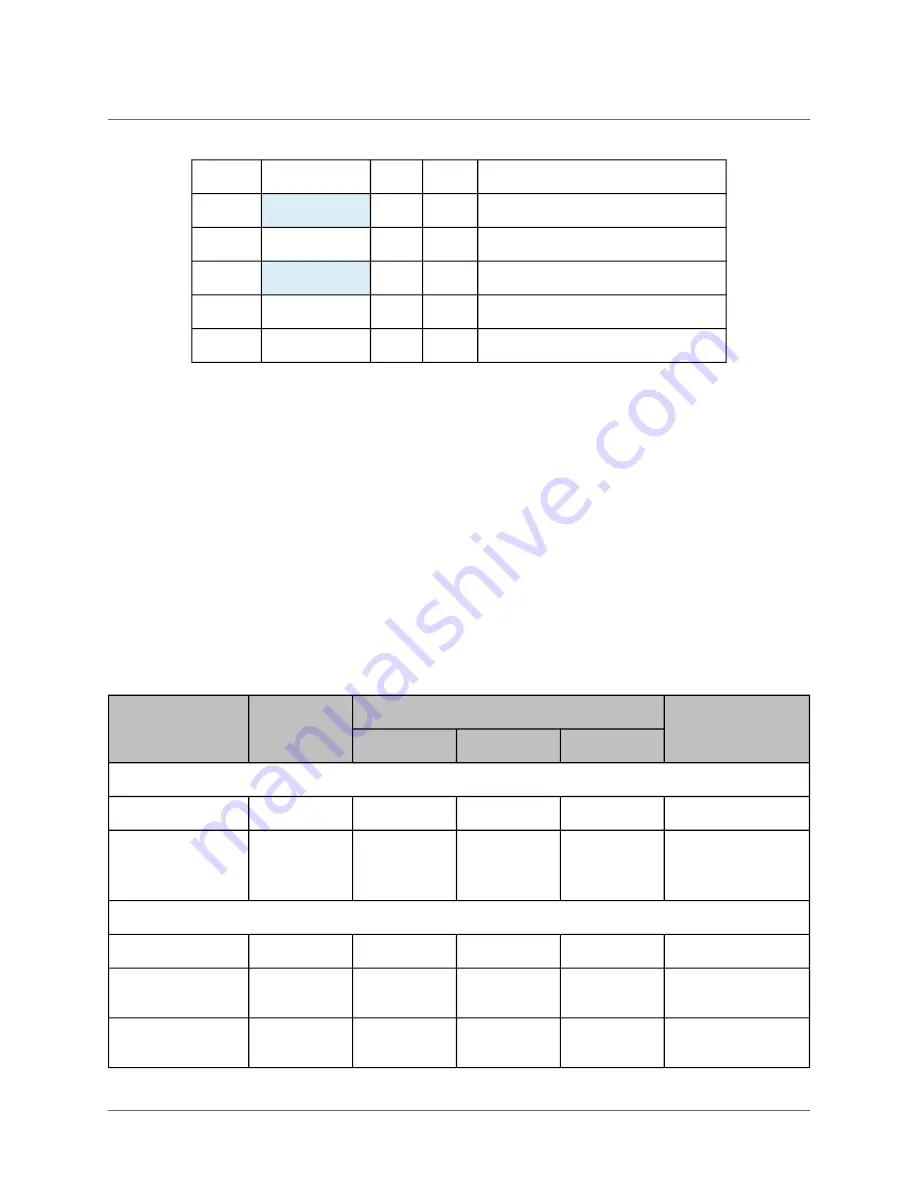

Table 11 summarizes the major clocks on the FE310-G000 and their initial reset conditions. At

power-on reset, the AON domain

lfclk

is clocked by either the LFROSC or

psdlfaltclk

, as

selected by

psdlfaltclksel

. At wakeup reset, the MOFF domain

hfclk

is clocked by the

HFROSC.

Table 11:

FE310-G000 Clock Sources

Frequency

Name

Reset

Source

Reset

Min

Max

Notes

AON Domain

LFROSC

lfroscrst

32 kHz

1.5 kHz

230 kHz

±45%

psdlfaltclk

-

-

0 kHz

500 kHz

When selected

by

psdlfaltclksel

MOFF Domain

HFROSC

hfclkrst

13.8 MHz

0.77 MHz

20 MHz

±45%

HFXOSC crystal

hfclkrst

ON

10 MHz

20 MHz

16 MHz on

HiFive

HFXOSC input

hfclkrst

ON

0 MHz

20 MHz

External clock

source

Table 10:

lfrosccfg: Ring Oscillator Configuration and Status

Chapter 6 Clock Generation

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 29