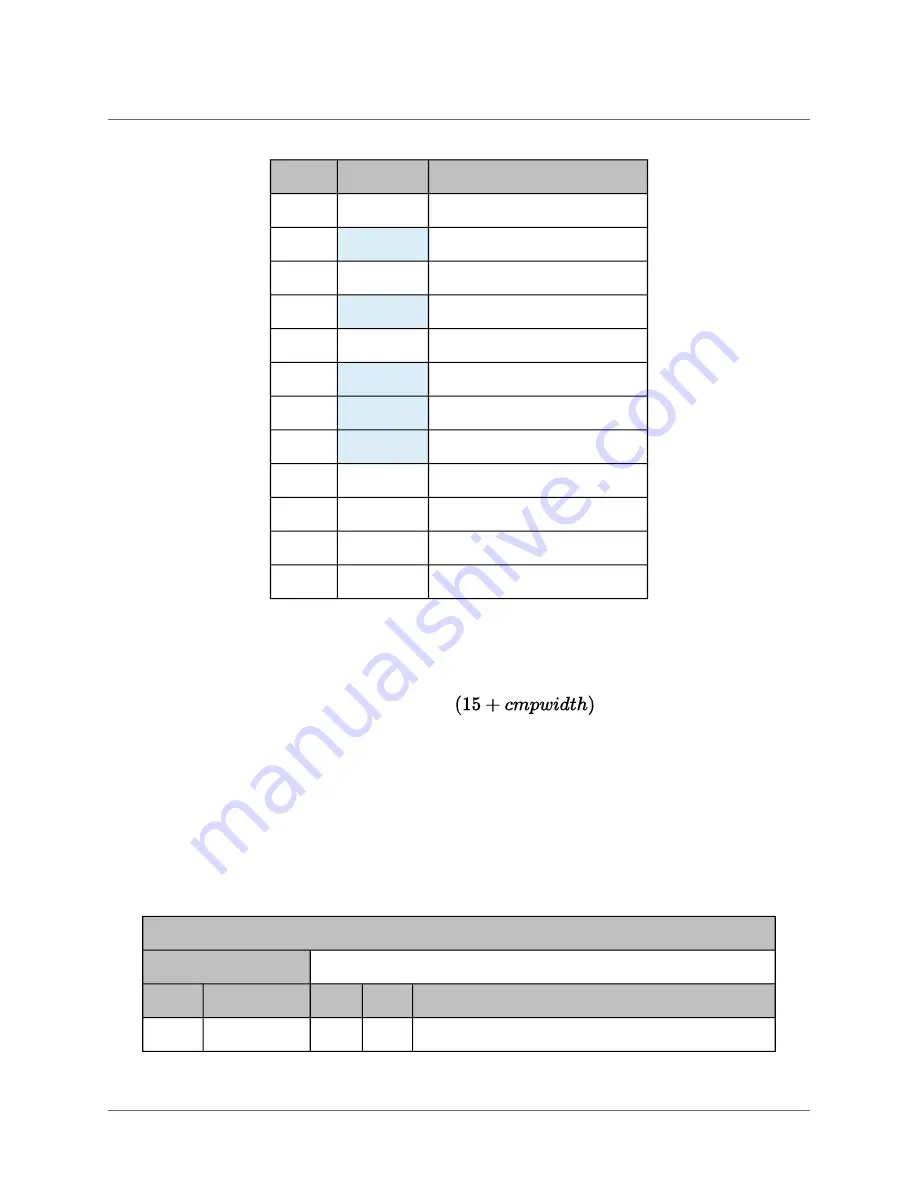

Offset

Name

Description

0x00

pwmcfg

PWM configuration register

0x04

Reserved

0x08

pwmcount

PWM count register

0x0C

Reserved

0x10

pwms

Scaled PWM count register

0x14

Reserved

0x18

Reserved

0x1C

Reserved

0x20

pwmcmp0

PWM 0 compare register

0x24

pwmcmp1

PWM 1 compare register

0x28

pwmcmp2

PWM 2 compare register

0x2C

pwmcmp3

PWM 3 compare register

19.4

PWM Count Register (

pwmcount

)

The PWM unit is based around a counter held in

pwmcount

. The counter can be read or written

over the TileLink bus. The

pwmcount

register is

bits wide. For example, for

cmpwidth

of 16 bits, the counter is held in

pwmcount[30:0]

, and bit 31 of

pwmcount

returns a

zero when read.

When used for PWM generation, the counter is normally incremented at a fixed rate then reset

to zero at the end of every PWM cycle. The PWM counter is either reset when the scaled

counter

pwms

reaches the value in

pwmcmp0

, or is simply allowed to wrap around to zero.

The counter can also be used in one-shot mode, where it disables counting after the first reset.

PWM Count Register (

pwmcount

)

Register Offset

0x8

Bits

Field Name

Attr.

Rst.

Description

[30:0]

pwmcount

RW

X

PWM count register.

cm 15

bits wide.

Table 83:

SiFive PWM memory map, offsets relative to PWM peripheral base address

Table 84:

PWM Count Register

Chapter 19 Pulse Width Modulator (PWM)

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 96