breakpoint register giving the address 1 byte above the breakpoint range, and using the

chain

bit to indicate both must match for the action to be taken.

NAPOT ranges make use of low-order bits of the associated breakpoint address register to

encode the size of the range as follows:

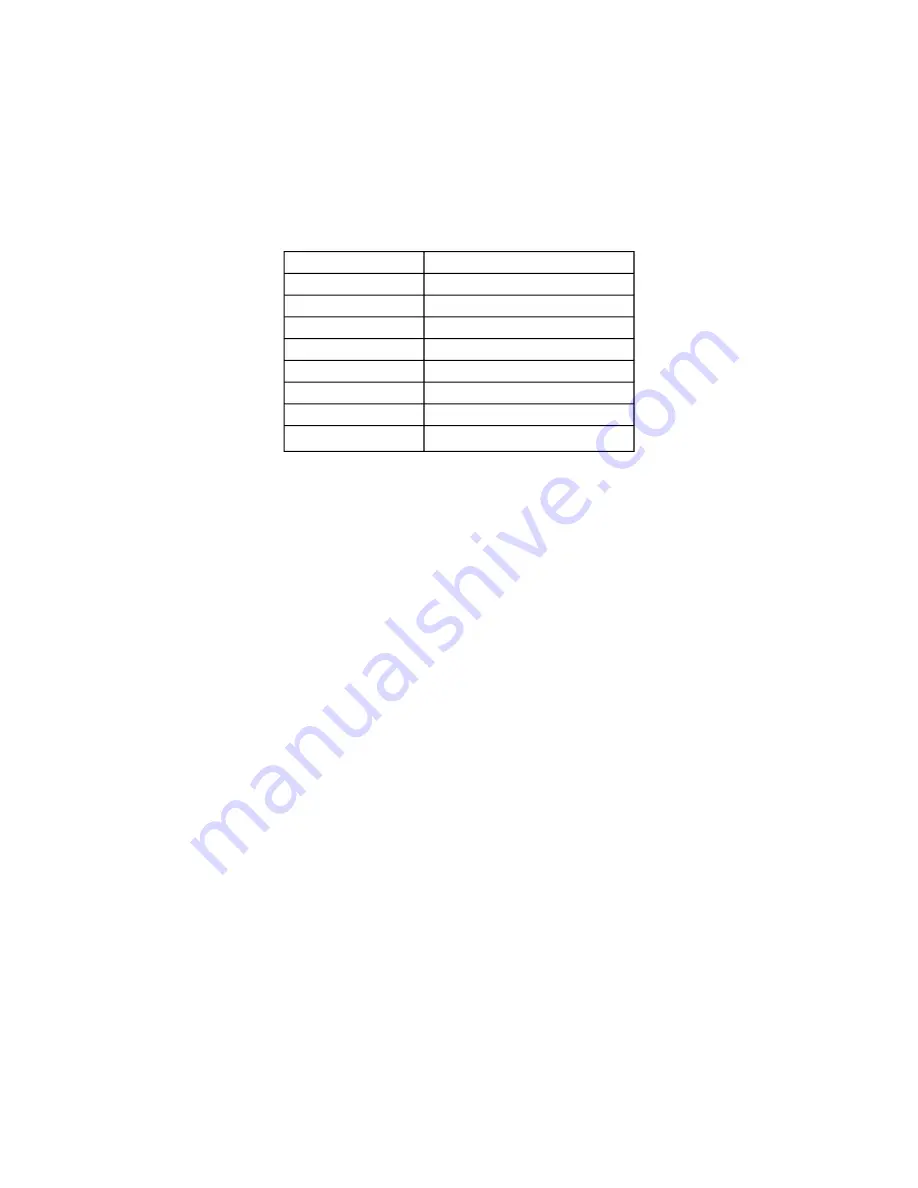

maddress

Match type and size

a…aaaaaa

Exact 1 byte

a…aaaaa0

2-byte NAPOT range

a…aaaa01

4-byte NAPOT range

a…aaa011

8-byte NAPOT range

a…aa0111

16-byte NAPOT range

a…a01111

32-byte NAPOT range

…

…

a01…1111

2

31

-byte NAPOT range

Table 106:

NAPOT Size Encoding

The

maskmax

field is a 6-bit read-only field that specifies the largest supported NAPOT range.

The value is the logarithm base 2 of the number of bytes in the largest supported NAPOT range.

A value of 0 indicates that only exact address matches are supported (1-byte range). A value of

31 corresponds to the maximum NAPOT range, which is 2

31

bytes in size. The largest range is

encoded in

maddress

with the 30 least-significant bits set to 1, bit 30 set to 0, and bit 31 holding

the only address bit considered in the address comparison.

To provide breakpoints on an exact range, two neighboring breakpoints can be combined with

the

chain

bit. The first breakpoint can be set to match on an address using

action

of 2 (greater

than or equal). The second breakpoint can be set to match on address using

action of 3

(less

than). Setting the

chain

bit on the first breakpoint prevents the second breakpoint from firing

unless they both match.

Breakpoint Match Address Register (

Each breakpoint match address register is an XLEN-bit read/write register used to hold signifi-

cant address bits for address matching and also the unary-encoded address masking informa-

tion for NAPOT ranges.

Breakpoint traps are taken precisely. Implementations that emulate misaligned accesses in soft-

ware will generate a breakpoint trap when either half of the emulated access falls within the

address range. Implementations that support misaligned accesses in hardware must trap if any

byte of an access falls within the matching range.

Copyright © 2019, SiFive Inc. All rights reserved.

108

Summary of Contents for FE310-G002

Page 1: ...SiFive FE310 G002 Manual v19p05 SiFive Inc ...

Page 11: ...Figure 1 FE310 G002 top level block diagram Copyright 2019 SiFive Inc All rights reserved 9 ...

Page 15: ...Chapter 2 List of Abbreviations and Terms 13 ...

Page 23: ...Chapter 4 Memory Map The memory map of the FE310 G002 is shown in Table 4 21 ...