......................................................................................... 24

One-Time Programmable (OTP) Memory

...........................................................24

Quad SPI Flash Controller (QSPI)

...................................................................... 24

................................................................................................. 25

....................................................................................... 25

...................................................................................... 26

Internal Trimmable Programmable 72 MHz Oscillator (HFROSC)

..................................26

External 16 MHz Crystal Oscillator (HFXOSC)

.............................................................27

Internal High-Frequency PLL (HFPLL)

........................................................................ 28

Internal Programmable Low-Frequency Ring Oscillator (LFROSC)

................................31

Alternate Low-Frequency Clock (LFALTCLK)

...............................................................32

..................................................................................... 36

Interrupt Control Status Registers

............................................................................... 37

..................................................................37

............................................................................ 37

......................................................................... 39

....................................................................... 39

................................................................................. 39

2

Summary of Contents for FE310-G002

Page 1: ...SiFive FE310 G002 Manual v19p05 SiFive Inc ...

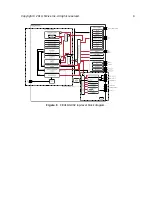

Page 11: ...Figure 1 FE310 G002 top level block diagram Copyright 2019 SiFive Inc All rights reserved 9 ...

Page 15: ...Chapter 2 List of Abbreviations and Terms 13 ...

Page 23: ...Chapter 4 Memory Map The memory map of the FE310 G002 is shown in Table 4 21 ...