Core-Local Interruptor (CLINT)

The CLINT block holds memory-mapped control and status registers associated with software

and timer interrupts. The FE310-G002 CLINT complies with

The RISC‑V Instruction Set Manual,

Volume II: Privileged Architecture, Version 1.10

.

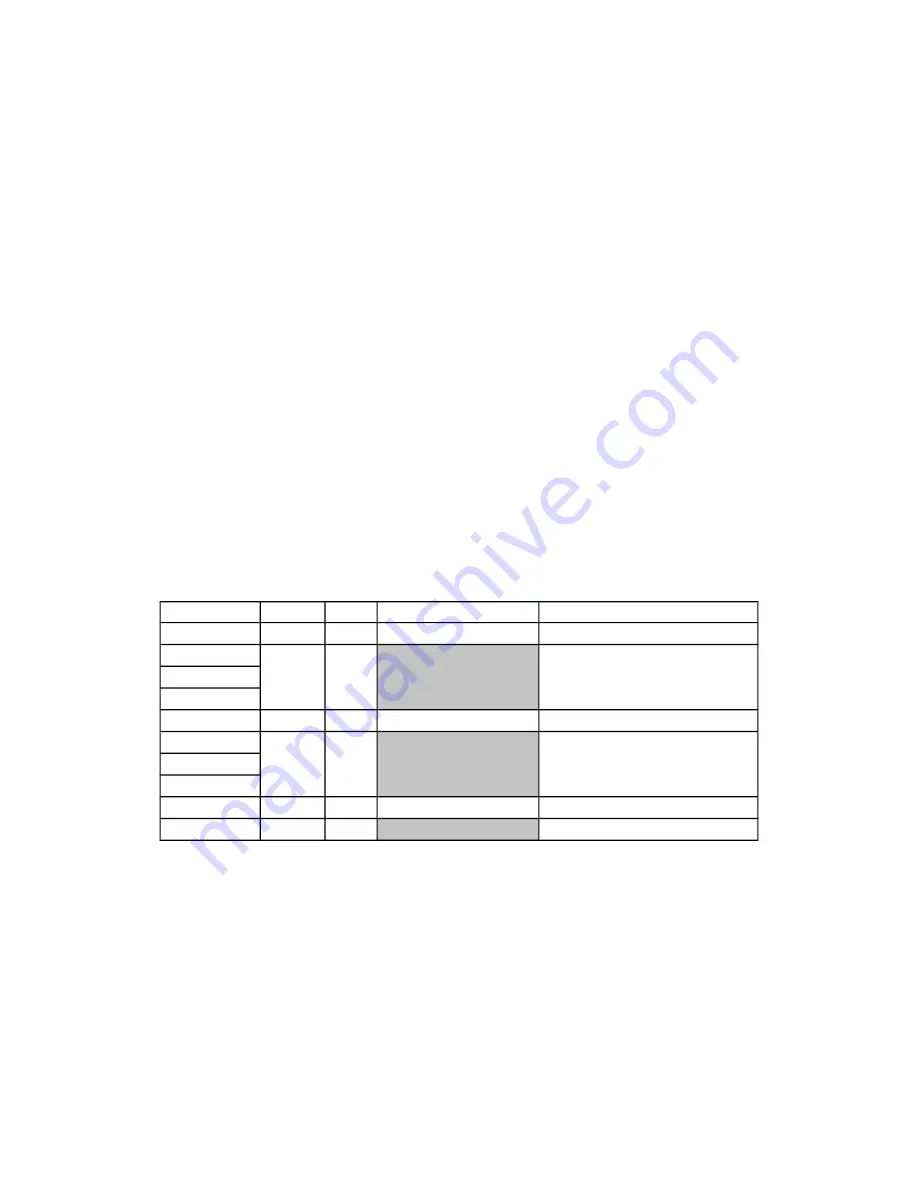

Table 24 shows the memory map for CLINT on SiFive FE310-G002.

Address

Width

Attr.

Description

Notes

0x2000000

4B

RW

msip

for hart 0

MSIP Registers (1 bit wide)

0x2004008

…

0x200bff7

Reserved

0x2004000

8B

RW

mtimecmp

for hart 0

MTIMECMP Registers

0x2004008

…

0x200bff7

Reserved

0x200bff8

8B

RW

mtime

Timer Register

0x200c000

Reserved

Table 24:

CLINT Register Map

Machine-mode software interrupts are generated by writing to the memory-mapped control reg-

ister

msip

. Each

msip

register is a 32-bit wide

WARL

register where the upper 31 bits are tied to

0. The least significant bit is reflected in the

MSIP

bit of the

mip

CSR. Other bits in the

msip

reg-

ister are hardwired to zero. On reset, each

msip

register is cleared to zero.

Software interrupts are most useful for interprocessor communication in multi-hart systems, as

harts may write each other’s

msip

bits to effect interprocessor interrupts.

42

Summary of Contents for FE310-G002

Page 1: ...SiFive FE310 G002 Manual v19p05 SiFive Inc ...

Page 11: ...Figure 1 FE310 G002 top level block diagram Copyright 2019 SiFive Inc All rights reserved 9 ...

Page 15: ...Chapter 2 List of Abbreviations and Terms 13 ...

Page 23: ...Chapter 4 Memory Map The memory map of the FE310 G002 is shown in Table 4 21 ...