Smart Machine Smart Decision

SIM2000S_Hardware_Design_V1.00

36

2014-02-27

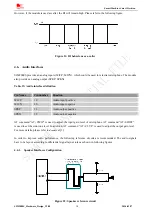

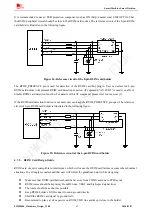

Figure 30: EXT CODEC to MODULE timing

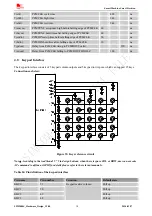

Figure 31: MODULE to EXT CODEC timing

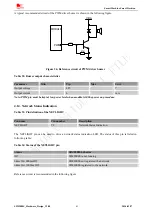

Table 22: Timing parameters

Parameter

Description

Min

Typ

Max

Unit

T(auxsync)

PCMSYNC cycle time

125

μ

s

T(auxsynch)

PCMSYNC high time

62.4

62.5

μ

s

T(auxsyncl)

PCMSYNC low time

62.4

62.5

μ

s

T(auxclk)*

PCMCLK cycle time

7.8

μ

s

T(auxclkh)

PCMCLK high time

3.8

3.9

μ

s

T(auxclkl)

PCMCLK low time

3.8

3.9

μ

s

T(suauxsync)

PCMSYNC setup time high before falling edge of

PCMCLK

1.95

μ

s

T(hauxsync)

PCMSYNC hold time after rising edge of PCMCLK

1.95

μ

s

T(suauxdin)

PCMDIN setup time before falling edge of PCMCLK

70

ns

T(hauxdin)

PCMDIN hold time after falling edge of PCMCLK

20

ns

T(pauxdout)

Delay from PCMCLK rising to PCMDOUT valid

50

ns

Note: T(auxclk) = 1/(128 KHz).