SiRFatlasV

Hardware Design Guide

January, 2010

SiRF Design Guide

– Proprietary and Confidential

10

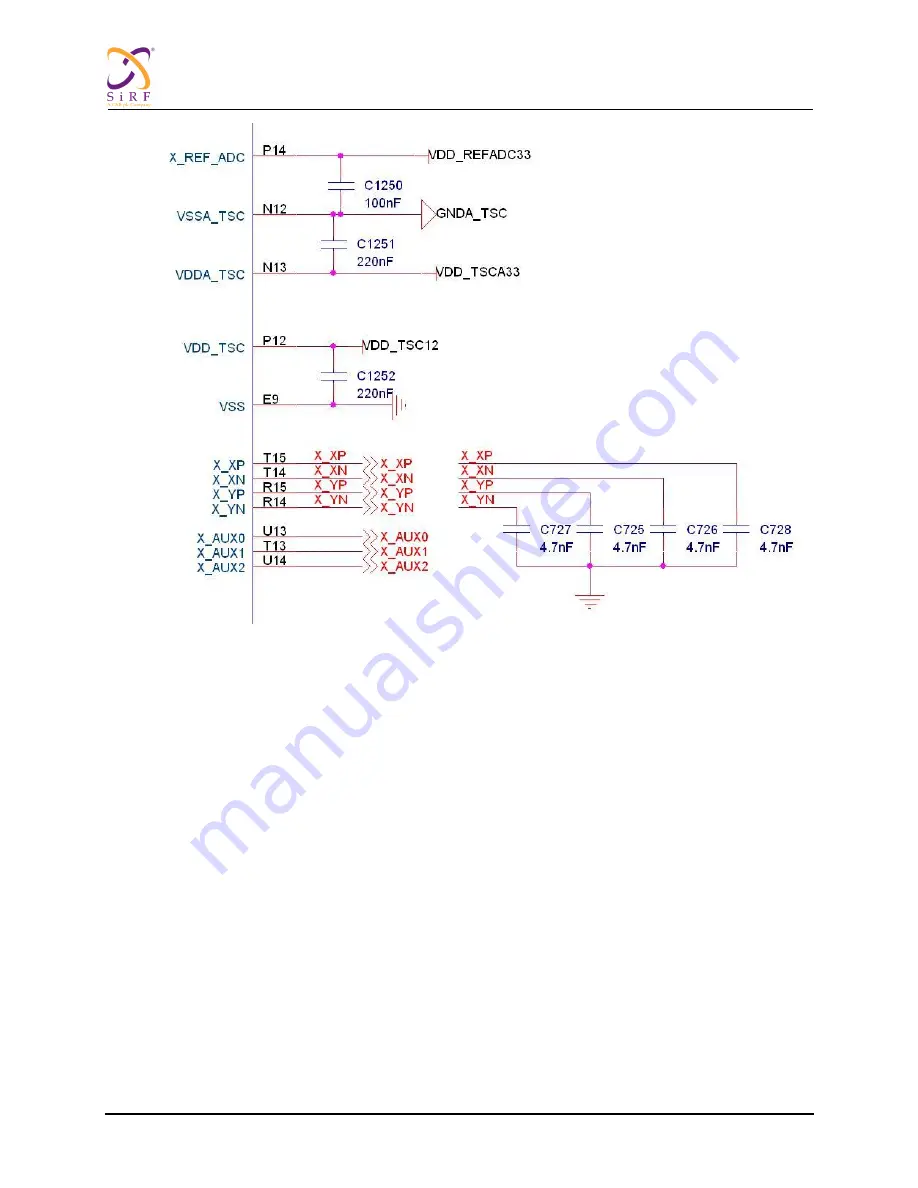

Figure 4: ADC Power Supply and Reference Decoupling

SD/MMC

Add an external pull-up resistor to all data and command signals when using an SD/MMC card or an

iNAND/moviNAND card.

Use SD0 but not SD2 as the boot media.

For MMC/ moviNAND, the pull-up resistor should be:

50 kOhm ~ 100 kOhm for the DATA net

4.7 kOhm ~ 100 kOhm for the CMD net

For SD/iNAND, the pull-up resistors to all data and command signals should be 10 kOhm ~ 100 kOhm.

Add a quick discharging circuit by pulling the SD0's power low to GND with a 1 kOhm resistor when SD0

is in power-down state (see R307 to Q303 in Figure 5

.) The reason for doing this is:

The iNAND may not reboot normally if it did not discharge after power-off.