SiRFatlasV

Hardware Design Guide

January, 2010

SiRF Design Guide

– Proprietary and Confidential

14

Behavior

X_RTC_RST_

B

On_Key 15s

X_RESET_B

Warm-

Reset

Power off logic through x_system_en

and x_dram_en

Yes

Yes

No

No

RTC time loss

Yes

Yes

No

No

SoC logic is reset when system running

Power-off

Power-off

Yes

Yes

SoC logic is reset when system is in

deep-sleep or hibernation

Power-off

Power-off

No

No

Reboot when system is running

No (press

On_key again)

No (press

On_key again)

Yes

Yes

Reboot when the system is in deep-sleep

or hibernation

No (press

On_key again)

No (press

On_key again)

No

No

Table 5: Reset Behavior when Working as a Reset Button

A

VOID

I/O

L

EAKAGE

D

URING

S

O

C

P

OWER

-O

FF

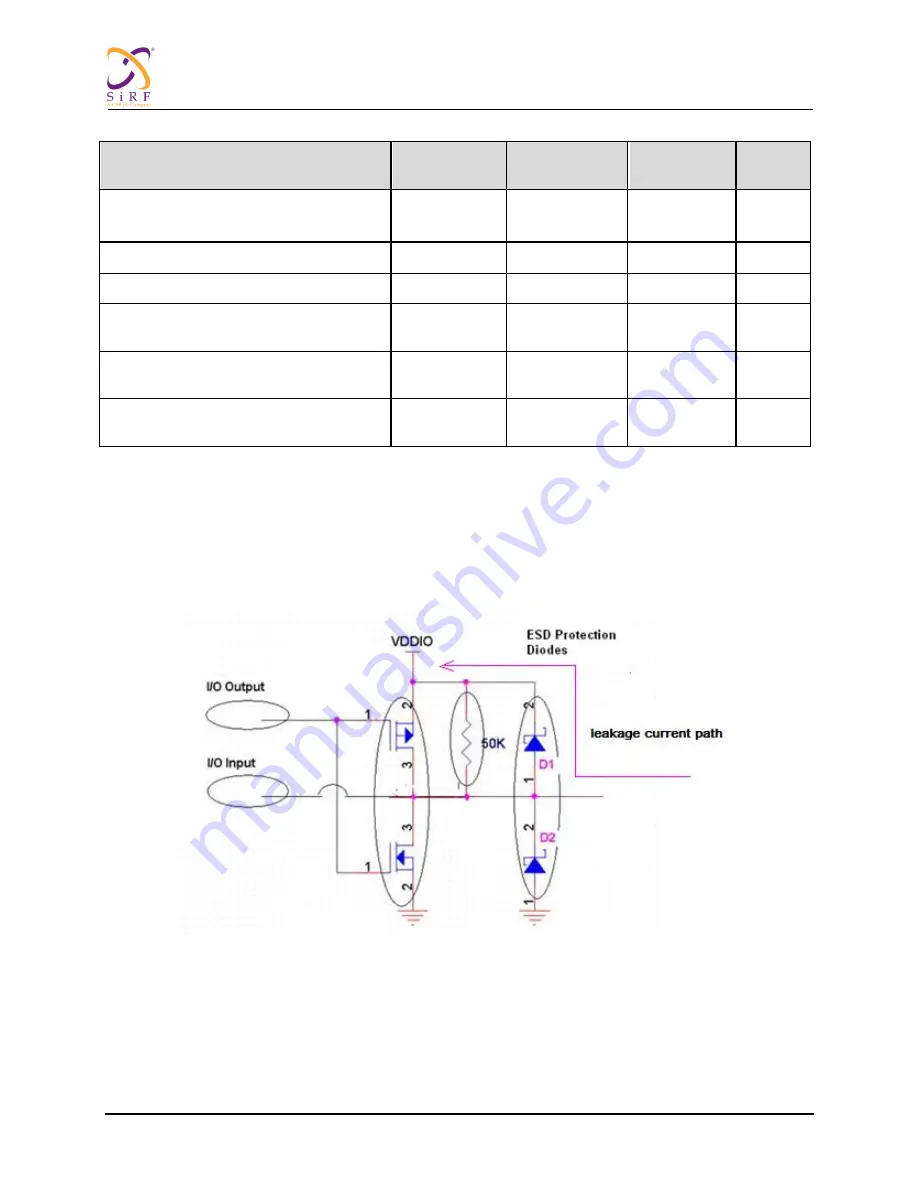

The SiRFatlasV SoC has an ESD protection circuit between the I/O pad

’s power and the I/O pad, when

the I/O pad is not powered there is an external source to drive this pad

“high” or “toggle”, therefore there

may be leakage from the external source to the I/O power, and this may result in system instability.

Figure 8: P-MOS and N-MOS in I/O Pad